嵌入式运行速度高,系统较复杂,常常集成超大规模FPGA器件、DSP器件、DDR存储器以及各种接口电路。这对电源的输出电压值、功耗、电压精度、上电顺序以及电源完整性提出更高的要求。

这里介绍一种基于CPCI的嵌入式单板计算机电源的设计方案。该设计主要应用于航空设备和军用车载设备。

2、系统电源需求分析与器件造型

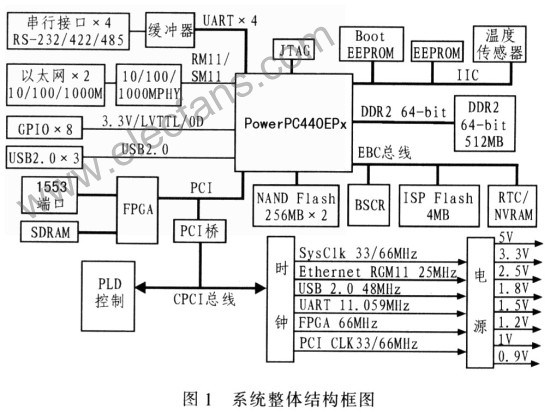

图1为系统整体结构框图。该系统由CPU和与其相连的DDR储存器、PCI接口、时钟、电源、EBC总线以及外部接口电路组成。CPU采用AMCC公司的PowerPC 440EPx。

2.1 系统电源需求

该系统电源较复杂,有多达8种不同的电源电压值,其中5 V和3.3 V由CPCI机箱提供。5 V供给DC/DC器件降压以产生其他电源电压,同时给1553总线的变压器供电。3.3 V是系统主电源,包括USB PHY、时钟器件、FPGA和CPU以及PCI桥器件(PLX6466)的I/O部分等。其他电源电压都是由5V或3.3 V经电源器件降压得到。

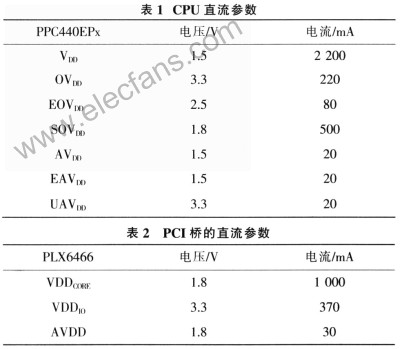

表1、2分别为CPU和PCI桥器件的功耗需求,CPU器件对上电顺序没有要求。其中VDD 1.5 V是PPC440EPx的内核电压,SOVDD是CPU的DDR2接口电源;1.8 V为PCI桥的内核电压,VDDIO是PCI桥的接口电源。

该系统采用DDR2作为内存,使用4片Micron公司的MT47H64M16,容量为512 MB。每片DDR2器件的内核、接口和DLL的电源电压都是1.8 V,最大电流为440 mA。另外需特别注意DDR2的VREF以及地址和控制信号的端口接电压VTT,其电压值都是0.9 V。其中,VREF对容差的要求非常严格(小于2%),不过其对电流的要求较小。而对VTT不仅有严格的容差要求,而且还要求其能在瞬间输出或吸收很大的电流。同时,VREF岍要随着VDD的变化而变化,VTT也要跟踪VREF的变化。通常的LDO难以完成这样的工作,必须采用专用的DDR端接电源器件。

该系统使用Spartan3型FPGA器件XC3S200实现1553收发器以及一些接口电路的设计。该器件使用3个电压内核电压VCCINT(1.2 V),辅助电压VCCAUX(2.5 V)以及接口电压VCCO(3.3 V)。FPGA内部有上电复位电路,只有当这3个电源信号都达到各自门限电压,才释放该复位信号。因此,对这3个电源信号的上电顺序没有要求。不过,如果 VCCINT先于VCCAUX上电,则会在上电时额外增加几百毫安的瞬时电流。估计FPGA器件功耗可采用基于电子数据表的工具XPower EsTImator(XPE)或在ISE下直接调用XPower。系统利用XPower软件估计出该设计功耗需求:VCCINT为50 mA,VCCAUX为10 mA。系统使用两片88E1111作为千兆以太网的PHY器件,该器件以2.5 V为砌电压(410 mA),1.0 V为内核电压(250 mA)。除上述集成电路外,系统还有诸如串行接口、USB接口、时钟等电路,但功耗都较低。从分析可知:1.5 V和1.8 V需要使用大功率的电源器件,DDR2的电源需要专用的电源器件,其他电压的功率要求较小。

2.2 电源器件选型

电源器件主要分为线性稳压器和DC/DC转换器两大类型。LDO属于线性稳压器主要应用于输人和输出压差较小的场合,其特点是:成本低、噪音低、静态电流小、需外接元件少,但其转换效率不是很高,且输出电流一般不是很大。DC/DC转换器的转换效率高、输出大电流、静态电流小。但由于采用PWM控制,其开关噪音较大,成本也相对较高。且外接电路较复杂,一般都需外接开关管、电感及电容。许多新型 DC/DC将开关管集成到器件内部.因此只需外接电感和滤波电容。

根据电源器件的特点,以及对系统电源需求的分析,这两种类型的电源器件在该系统都得到使用。但为简化设计、便于批量生产和物料管理,该系统只使用3个不同型号的电源器件,分别是:LT3501、LDO器件TPS51100和TPS74801。其中,功耗需求较大的1.5 V和1.8 V电源电路采用LT3501实现;DDR2的端接电源和参考电源由器件TPS51100提供;系统的其他电源由TPS74801提供。

3、系统硬件电路设计

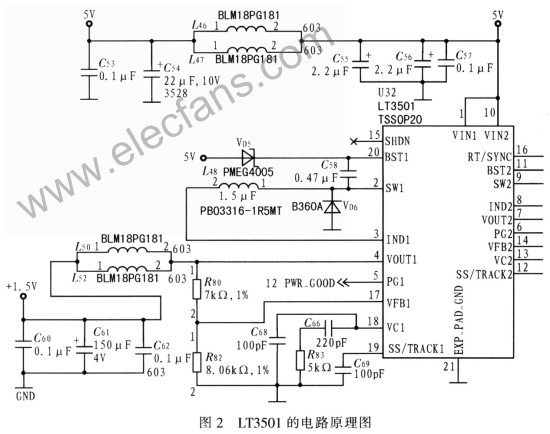

由于LDO电路简单及篇幅原因,这里重点讨论LT3501的电路设计,图2为LT3501的电路原理图。

3.1 参数配置

3.1.1 输出电压

输出电压值的选择较简单,由连接在VOUT和VFR间的2只电阻分压得到。其公式为:

![]()

图2中,分压电阻为2只精度为1%的电阻R680和R682(分别对应R1,R2),代入式(1),计算其输出电压VOUT=1.495 V。

3.1.2 开关频率

LT3501的开关频率由连接在RT/SYNC引脚上的电阻决定,如图3所示。当电阻从15.4 kΩ增加到133 kΩ时,其开关频率从1.5 MHz减小到250 kHz。为减小外连的电感和电容的尺寸,便于PCB设计,开关频率选择较高的f=1.2 MHz。则根据图3所示曲线,其电阻值为20.6 kΩ。

3.1.3 电感值

对于开关电源,电感的取值非常重要。根据LT3501的数据手册公式:

![]()

式中,DC指占空比,其最小值DCMIN=tON(MIN)&TImes;f=0.24。VD是捕捉二极管的正向压降,其值约为0.4 V。

假如最大输出电流需3 A,由式(2)可计算电感L至少为1.2μH。

为提高效率,减小输出纹波,要求电感:额定电流的有效值应大于最大负载电流;同时其饱和电流值应大于30%;直流电阻值应小于0.05 Ω,其电感值应大于理论值。据此,系统选择PB03316-1R5MT,该电感的电感值为1.5μH,直流电阻为0.010Ω,额定电流有效值为8.0 A,饱和电流为6.4 A。选定电感值后,就可将其代入式(2)计算纹波电流△IL为0.8 A。

3.1.4 输入电容和输出电容

由于开关电源的输入是以脉冲形式为输出提供电流,并且其上升和下降时间非常快。

因此。需用输入电容滤出电压纹波,以减小EMI。并可使用4.7μF或更大的X7R或X5R型电容旁路输入信号,也可使用钽电容和较小容量的陶瓷电容并联来实现。陶瓷电容应尽可能靠近器件的输入引脚。

输出电容滤波流过电感的电流,以得到纹波很小的输出电压。同时,其储能功能还可满足瞬间负载,并稳定LT3501的控制环路。LT3501的控制环路采用电流模式,对输出电容的RESR(串连等效电阻)没有要求。

因此,可以采用陶瓷电容来作输出电容。输出电容的值可以根据式(3)估算。其中MLS(Max Load Step)为最大电流负载的跳变,例如:该系统MLS为3A。

输出电压的纹波可按式(4)和(5)估算:式(4)计算陶瓷电容,式(5)计算钽电容或铝电解电容。系统采用温度特性较好的X7R型陶瓷电容与钽电容并联。利用式(4)计算出纹波电压约0.56 mV,满足CPU和其他电路对电源纹波的要求。

3.2 PCB布局

对于开关电源,PCB的布局非常重要。当开关电源工作时,电路的部分支路存在很大的阶跃电流。该电流主要在器件内部的开关管、外面的环流二极管和输入电容之间流动。由这些元件构成的环路应尽可能的小。在布局时,这些器件以及电感和输出电容应该布局在电路板的同一层,其连线也尽可能在同一层完成。在这些元件的下面,有一块连续的局部地。该局部地与系统地的连接采用单点连接方法,连接点最好选在输出电容的接地端。另外,SW和BST信号的布线要尽可能的短。 LT3501器件的底部有裸露的leadframe,该结构散热良好。在设计PCB时。可在器件底部的对应位置放一块覆铜,并通过多个过孔与内层的大面积覆铜连接。

4、结论

分析该系统的功耗,在考虑一定冗余的基础上,利用3种电源器件设计该嵌入式系统的电源电路。并使用MAX705电源监控器件提高系统的可靠性。该系统已成功在多个实际应用中得到验证,并且表现良好。