在当今世界,高科技手持式设备广为流行,你或许会以为并行数据接口是一件过时的东西。毕竟这种架构已面市数十年,对于如今关注小尺寸、低功耗、功能丰富的市场来说,它不再被视作未来发展的候选技术。然而,仍有许多新型移动电话和MID设计继续采用这种旧有接口,因为它是应用处理器的唯一可用接口。

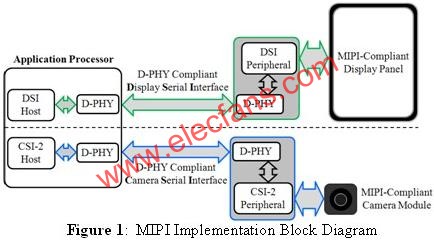

当前,终端市场要求新设计具有更低功耗、更高数据传输率和更小的PCB占位空间,在这种巨大压力之下,一些智能化且具有更高性能价格比的替代方案开始逐渐为相关设计人员所采用。现在使用的几种基于标准的串行差分接口当中,MIPI接口在功率敏感同时又要求高性能的移动手持式设备领域中的增长极为迅速。而基带和显示器/相机模块对MIPI显示器串行接口(Display Serial Interface,DSI) 和相机串行接口(Camera Serial Interface,CSI-2)协议的广泛采纳,正是这种增长的主要推动力。DSI 和 CSI-2是分别针对显示器和相机要求的逻辑层(logical-level)协议,它们通过物理互连对主机与外设之间的数据进行管理、差错和通信。 MIPI D-PHY规定了连接处理器和外设的物理层的物理及电气特性,这些MIPI接口为服务移动设备市场而专门设计。图1所示为显示器与相机路径上的MIPI接口的顶层模块示意图。

图1:MIPI实现方案模块示意图

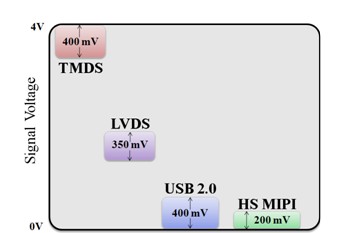

这里举两个MIPI获大规模采纳的例子,包括两大主流芯片组制造商英特尔(Intel)和Marvell都在它们最新的移动芯片架构中集成了MIPI功能,英特尔的Moorestown处理器和Marvell的Armada 600处理器都采用了基于MIPI标准的 DSI 或 CSI接口。MIPI 架构可通过减少其差分串行接口中的I/O 数目来降低处理器的引脚数目及功耗,故是当仁不让的最佳选择。动态可调的低功耗 (LP) 和高速 (HS) 数据模式以及高速模式下的低信号摆幅(signal swing),也可为MIPI 提供比单端接口更好的EMI辐射性能和EMI抗扰性能。此外,由于连线减少,PCB设计灵活性得以提高,从而能够改进连接器或外设器件的布局。虽然这些优点为许多串行接口所共有,但MIPI 是专门在高速(数据传输)模式下采用低振幅信号摆幅,针对功率敏感型应用而量身定做的。图2比较了MIPI与其它差分技术的信号摆幅。

图2:几种流行的差分摆幅(differenTIal-swing)技术的信号振幅比较

这种架构的另一个主要特性是可扩展性。MIPI规定了一个差分时钟通道(lane)和一个从1到4数量可扩展的数据通道,可根据处理器和外设的需求来调节数据率。而且,MIPI D-PHY规范只给出了数据率范围,并没有规定具体的工作速率。在一个应用中,可用的数据通道和数据率都由接口两端的器件决定。不过,目前可用的MIPI D-PHY IP内核可提供每数据通道高达1 Gbps的传输率,这种特性无疑意味着MIPI完全适用于当前及未来的高性能应用。

采用 MIPI作为数据接口还有一大好处。由于MIPI DSI 和 CSI-2架构为新设计带来了灵活性,并支持XGA显示和高于8百万像素相机等令人瞩目的功能,故MIPI非常适合于新的智能电话和MID设计。有了具备 MIPI功能的新处理器设计提供的带宽能力,现在就可以考虑利用单个MIPI接口来实现高分辨率双屏显示和/或双相机等新颖功能了。

在采用了这些功能的设计中,针对MIPI信号进行设计和优化的高带宽模拟开关,如飞兆半导体公司的FSA642,可用于多个显示屏或相机组件之间的切换。 FSA642是一款高带宽三路差分单刀双掷 (SPDT)模拟开关,能够实现两个外设MIPI器件之间共享一路MIPI 时钟通道和两路MIPI数据通道。这样的开关可以提供一些额外的优点:对未选择器件的杂散信号(stub)进行隔离,并提高布线和外设布局的灵活性。为了确保MIPI互连路径上的这些物理开关的成功设计,除带宽之外,还必须考虑以下一些主要的开关参数:

1. 关断隔离:为了保持有源时钟/数据路径的信号完整性,要求开关具备高效的关断隔离性能。对于200mV、最大共模失配(common-mode mismatch)5mV的高速MIPI差分信号,开关路径之间的关断隔离应该为-30dBm或更好。

2. 差分延迟差:差分对内部信号间的延迟差(skew)(差分对内延迟差)和时钟与数据通道差分交叉点之间的延迟差(通道间延迟差) 必需降至50 ps或更小。对于这些参数,这类开关的业界同类最佳延迟差性能目前在20 ps 到 30 ps之间。

3. 开关阻抗:在选择模拟开关时,第三个主要考虑事项是导通阻抗(RON) 和导通电容 (CON)的阻抗特性的折衷选择。MIPI D-PHY链路同时支持低功耗数据传输和高速数据传输模式。因此,开关的RON应该平衡选择以优化混合工作模式的性能。理想情况下,这一参数应该分别针对每一个工作模式而设定。结合每一模式的最佳RON,并保持很低的开关CON对保持接收端的压摆率(slew rate)十分重要。一般规则是,使CON 低于10 pF将有助于避免高速模式下通过开关的信号转换时间的恶化(延长)。

随着MIPI接口架构逐渐被移动平台所采用,设计人员最终可能淘汰原有的并行接口,相比以往数代设计,这种替代方案能够节省功率、空间和成本,同时帮助终端客户提高生产率,并为他们带来更令人满意的体验。下一代必备移动设计创新的关键在于充分利用带MIPI功能的处理器和外设所提供的灵活性和功能。