1 引言

随着嵌入式微处理器和嵌入式操作系统的发展,嵌入式系统在通讯、控制和消费电子等诸多领域得到了广泛的应用。嵌入式系统通常是面向特定应用的嵌入式CPU,与通用型的最大不同就是嵌入式CPU大多工作在为特定用户群设计的系统中,它通常都具有低功耗、体积小、集成度高等特点,能够把通用CPU中许多由板卡完成的任务集成在芯片内部,从而有利于嵌入式系统设计趋于小型化,以动能力增强,与网络的耦合也越来越紧密。

本文利用ARM嵌入式系统构造微型化的工程地震仪雏形,以满足特定条件的工作需要,降低功耗,节省能源以延长工作时间,减小仪器尺寸和重量,使仪器更为轻便。

2 现有工程地震仪简介

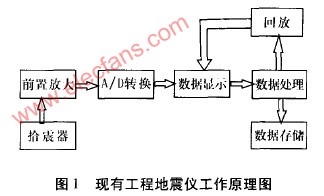

工程地震仪应用于地基、路基与基础工程检测;隧道工程检测;大中型水库的运行观测;桥梁工程检测;环境与地质灾害检测与评价等工程领域的地震检测任务l2 。一般来讲工程地震仪器利用锤击、电火花或爆炸等作为激发震源,硬件上由前置放大器,数据采集卡,A/D转换器,工控机(便携式微机)等部分组成。而数据采集,数据处理,分析软件都存储在工控机内,可以随时处理现场所采集的原始数据,发现问题及时处理。其功能一般有:瞬态多点端雷波勘探浅层反射测量浅层折射测量波速(剪切波)测量多波高密度地震映像桩基检测土建工程质量检测场地常时微动测量震动爆破测量。如图1 所示

其中,数据的显示,数据的处理和存储都是用工业控制微机来完成的,下面是一款典型的现有工程地震仪器工业控制微机的硬件配置:

CPU :PIII 500MHz

内存:128MB

硬盘:不小于40GB

光驱:内置

显示屏:800×600点阵VGA液晶显示屏(TFT真彩)

输入设备:触摸屏输入、精致小键盘、光电鼠标

接口:双串一并、双USB口、鼠标口、键盘口等标准口

移动存储:256M电子U盘

现有工程地震仪由于工控机功耗较高,体积尺寸大,野外携带不很方便,尤其是当野外工作需要电池支持时,受功耗的影响工作时间可能受一定的限制。对于某些特定场合,如煤矿井下作业时要考虑到防爆因素,必须在仪器外装加防爆外壳,而防爆因素与功耗,体积等密切相关,这便要求有相对功耗小,体积重量小的微型工程地震仪的出现。

3 系统硬件设计

3.1 工作原理

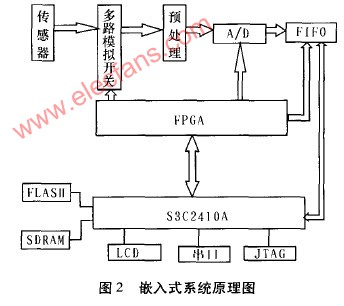

系统硬件主要分为ARM处理器模块、协处理器FPGA模块、预处理和A/D模块、通用外设模块4个部分,ARM处理器和现场可编程门阵列(FP.GA)共同组成监控系统的核心处理单元。现场勘探检测时,可利用爆炸的方式作为激发震源,当一次爆炸启动后,传感器信号通过模拟开关,先经过前置放大和滤波等预处理,获取符合A/D转换芯片要求的信号,经过A/D转换,进入FIFO,然后由嵌入式微处理器读取并处理数据,然后将数据存储到SIM卡或USB存储设备中。在A/D转换模块中,采用多路模拟开关,可完成大数量点的数据采集。FPGA是整个系统的控制中心,控制采集通道的切换,A/D转换芯片的启停,转换后的数据在FIFO中的存放以及向主处理器$3C2410A产生中断请求读取FIFO中的数据。如图2所示。

3.2 硬件介绍

3.2.1 协处理器模块

系统的协处理器采用Xilinx公司的FPGA,型号为SPARTANIIE XC2SIOOE。该芯片共有2700个逻辑单元,10万个逻辑门,片内块RAM为40KB。其具体实现以下功能:

· A/D模块读/写时序控制;

· 生成FIFO,其主要功能是存储经A/D编码的数据:

· 提供ARM处理器控制信号。

FPGA芯片分4部分来实现上述功能:

(1)内部控制信号产生器

FPGA对50 MHz时钟分频产生A/D芯片采样时钟Sampleclk和ARM处理器外部时钟Sysclk;Sysclk经锁相环电路(PLL)后产生ARM处理器工作所需的时钟信号 。

(2)ARM控制器

提供ARM处理器正常工作所必须的各种控制信号;实现ARM处理器地址总线、数据总线和外部中断信号接入 。

(3)A/D控制器

控制A/D模块的数据转换。产生A/D转换起始信号(/HOLD),检测数据转换完成信号(/EOC),产生FIFO写入信号,实现数据转换通道选择。

(4)FIFO存储器

生成FIFO,完成A/D转换数据的存储。

3.2.2 ARM处理器模块

ARM 处理器模块由FLASH、SDRAM 和s3C2410共同构建。系统选用Samsung公司的K9F1208UOA构建8位FLASH 存储器系统。K9F1208UOA单片容量为64 MB;选用两片单片容量32 MB。数据宽度为16位HY57V561620CT,并联构建32位SDRAM存储器系统,共64 MB的SDRAM空问可以满足嵌入式操作系统和各种复杂算法的运行要求。ARM处理器对各模块的控制则是通过底层驱动控制协处理器FPGA产生各种控制信号来实现。

3.2.3 预处理和A/D模块

传感器传播的模拟信号比较微弱,需要经过前置放大等预处理后方具备数据有效性。预处理主要是由前置放大电路构成,A/D模块主要由模拟开关和A/D转换芯片构成。模拟开关采用AD公司的AD7506,可实现12通道数据采集。A/D转换芯片采用CIRRUS公司的CS5381,是120dB、192kHz高性能立体声24位Σ 一△ A/D变换器,内置双极性电路构成的混合集成转换显片,具有外接元件少,功耗低,精度高等特点,并且具有自动校零和自动极性转换功能,只需外接少量的阻容件即可构成一个完整的A/D转换器。

3.2.4 接口和显示模块

包括常用的接口和显示器件。接口包括常用的串口等,用以进行数据的外部存储。显示模块主要包括构成操作的LCD和触摸屏等外围显示设备。

4 嵌入式系统软件设计

软件部分分为FPGA控制程序和ARM处理器两部分,FPGA用VHDL来设计,基于s3C2410A的软件设计主要任务有数据采集的驱动程序,操作系统的移植以及上层应用软件的设计。嵌入式操作系统应用WinCe.net,上层应用软件开发使用Em-bedded Visual C++,底层驱动和ARM处理器的调试则使用c语言。

系统开始工作后ARM处理器和FPGA协处理器中的FIFO开始初始化。经A/D转换后的数据存入对应的FIFO中。FIFO中的数据容量达到一定限度即产生巾断,ARM处理器中的主程序产生中断等待线程;一旦中断产生则进入中断服务程序,读取数据,之后进入ARM系统进行相应的处理,然后存储到存储设备。如图3所示。

4.1 嵌入式操作系统WindowsCE.net的裁减

使用集成开发环境Platform Builder根据提示完成操作系统镜像的定制、编译与调试工作,并可在此环境巾进行应用软件、驱动程序的开发。在ARM中植入Windows CE.net平台,首先根据目标设备的硬件配置及需要,对Windows CE.net进行基本定制,开发并安装驱动程序,增加必要的特性,生成镜像文件,通过JTAG将bootloader写入flash后,通过网卡将镜像文件下载到目标设备中,进行调试 同时要导出SDK,以备后面用EVC开发应用程序。

4.2 数据采集驱动程序

在数据采集中,主要对外部I/0口的访问,Wince的BSP都实现WRITE—PORT—UCHAR和READ— PORT— UCHAR函数。访问方式采用中断方式。WinCE把中断处理分为两部分中断服务例行程序ISR和中断服务线程,用户的中断处理主要在IST中完成 。。这里采用基于中断方式的非标准驱动,要实现两个步骤:编写中断服务线程IST和注册中断服务线程。中断信号由FIFO经FPGA不断产生,每发生一次中断,运行在核心态的中断服务例行程序就调用一次IST。

4.3 中断控制

系统如果对A/D转换数据采用实时读取的方式,则必然导致ARM处理器工作效率较低,所以在电路设计时采用中断方式。A/D模块输出数据以循环方式分别写入FIFO中。一旦FIFO中可使用数据容量减小到一定限度则产生中断,ARM处理器进入中断服务程序并读取FIFO中的数据。

4.4 上层应用软件

上层应用软件的开发包含以下模块:

数据采集系统:实施采集的控制和监测。

数据处理系统:简单处理采集到的数据,如数字滤波等。

图形显示系统:将采集到的数据以波形的形式显示在显示仪器L。

数据存储系统:构造数据存储系统,使数据以文件形式存入存储设备(FLASH闪存,USB外设,存储卡等),硬件上还要求支持USB通用串行总线,支持设备的热插拔,传输速度快.结构简单。

5 结束语

本文所研制的微型工程地震仪系统综合利用了嵌入式系统设计技术,与传统地震勘探设备相比大大提高了设备的便携性和节能性。同时,该系统注重数据快速存储的研究,并在实际系统中加以应用。本系统在设计时充分考虑了电路的灵活性和通用性,可根据不同的功能要求编写相应的VHDL语言程序。系统所使用的Windows CE操作系统可以任意裁剪,这对于功能的转换很有帮助。本系统已研制完毕,现处于现场实验阶段。随着计算机技术和网络技术的发展,嵌入式微处理器的性能的提高,嵌入式系统将在工业控制领域得到更广泛的应用。