设计中,根据IXYS公司IXFN50N80Q2芯片手册中提供的ID-VDS,ID-VGS和Cap-VDS等特性曲线及相关参数,利用saber提供的Model Architect菜单下Power MOSFET Tool建立IXFN50N80Q2仿真模型,图5-1所示MOSFET DC CharacterisTIcs设置,图5-2所示MOSFET Capacitance CharacterisTIcs设置,Body Diode 参数采用默认设置。

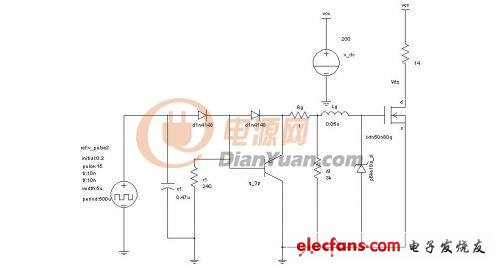

首先验证Rg、Vgs、Vds关系,仿真电路如图

?

这里电路中加入了一定的电感Lg,仿真电路寄生电感,取值是0.05uH,有没有什么依据?我当时是想导线计算电感的时候好像是要加上0.05u,就放了个0.05u。

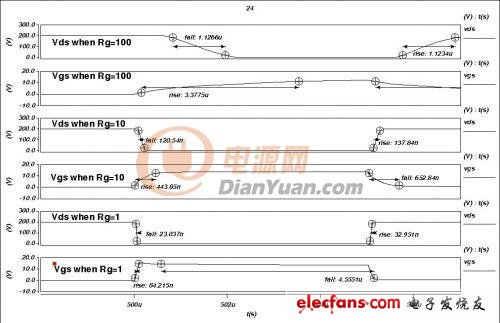

仿真过程是,Rg分别取1欧姆,到10欧姆,到100欧姆。验证Rg取值对驱动波形Vgs和开关导通特性Vds影响。结果如下图:

?

可以看出,不同Rg阻值对MOSFET IXFN50N80Q2 的影响。设计中,取Rg=10,取Rg=1,担心过冲击穿Vgs,取100,上升沿速度太慢,不满足高速应用。

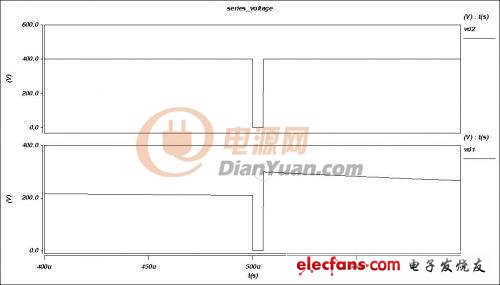

下边讨论MOSFET串联问题。仿真电路如图:仿真电路中两路驱动,只有Rg参数不一致,其他均一致。

?

Q2的驱动电路中Rg=15,Q1的驱动电路中Rg=10,这样的目的是在讨论驱动电路中等效电阻的不一致(可能来自Rg本身不一致,也可能是线路不同,器件不同而造成的不一致)情况下,对串联MOSFET导通过程影响。观察Vd1和Vd2两点的波形,如图:

?

从图中可以明显看到,由于驱动电路参数不一致Rg1

一般MOSFET串联都需要动态和静态均压。静态均压见图中的MOSFET两端并联电阻,取值可以参考MOSFET手册中关断状态的漏电流,通过静态电阻的漏电流是通过MOSFET静态漏电流的6倍左右,太大会加大电阻静态损耗。

本设计中动态均压网络,采用TVS并联在MOSFET两端,起到保护作用。TVS管好像有点贵,也可以采用RCD网络。有人说,TVS并联起到的不是动态均压作用,只是瞬态保护作用,这也是有道理的。

TVS管选择,就是Vwm 大于电路正常工作电压,Vc小于电路额定最大工作电压。

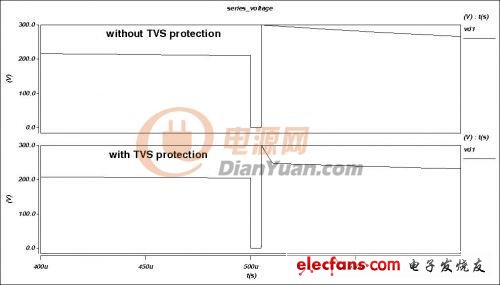

采用TVS管保护电路前后,Vd1仿真波形对比图:

?

可以看到,加入TVS管后,尖峰脉冲的持续时间大大缩短。

MOSFET串联应用,在保证动态静态均压和驱动一致性的条件下,还要采用一些隔离技术和多路驱动技术,以保证多只MOSFET串联组成高压大功率高频开关。这方面这里就不再写了,希望大家指点