摘要:本文介绍采用直接检测LDMOS 漏端电压来判断其是否过流的设计方案,给出了电路结构。通过电路分析,并利用BCD 高压工艺,在cadence 环境下进行电路仿真验证。结果证明:该方法能够快速、实时地实现过流保护功能,相比其它方法,在功耗、效率、工艺兼容性、成本等方面均有很大提高,可以直接应用于电源控制芯片中的安全保护设计。

1 引言

由于电源适配器芯片中内嵌集成或需要外部连接功率LDMOS 管,应用中的LDMOS 管又需要直接和高压相联接并通过大电流(目前的LDMOS 管已经能耐受数百乃至近千伏的高压)。因此,如何保障芯片和LDMOS 管的安全工作是芯片设计的重点之一。

利用片上二极管正向压降的负温度特性来监测芯片的热状态,进而控制功率LDMOS 管的开关是一种可行的安全设计方法。但是由于硅片存在热惰性,故不能做到即时控制。该方法更适宜作安全设计的第二道防线。

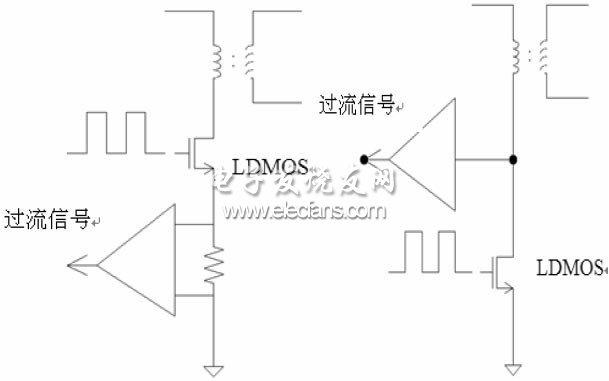

从芯片设计看,要确保适配器芯片使用的安全性,比较好的方法应该是直接监测流经LDMOS 管的大电流或LDMOS 管的漏极电压,以实时监控芯片的工作状态。一般采取两种方案:(一)在功率MOS 管源端对地串联一个小电阻用于检测源极电流,如图1(a)所示;(二)是通过检测电路监控LDMOS 的漏端电压,如图1(b)所示。前一种方案至少有以下缺点:(1)由于工艺存在离散性,电阻值很难做到精确(误差在20%左右);(2)源极串入电阻后,使原本导通电阻很大的LDMOS 管的管压降进一步增大,功率处理能力变弱;(3)电阻上流过大电流,消耗了不必要的能量,降低了开关电源的转换效率。

?

图1(a)串联电阻检测电流图1(b)直接检测漏端电压

而采用后一种方案,因为利用了集成电路的特点(电压采样电路的电阻比精度很容易做到1%),电路处理并不太复杂。重要的是LDMOS 管没有源极串联电阻,可减少能量损耗,不影响LDMOS 管的功率处理能力,提高了电源转换效率。

直接检测漏端电压判断LDMOS 是否过流的设计思想是在LDMOS 管导通时,通过采样电路检测LDMOS 漏端电压,经比较,过流比较器输出一个低电平过流信号以关闭LDMOS 管;而在LDMOS 管截止期间,采样电路不工作,同时为了提高可靠性将比较器窗口电平适度拉高。

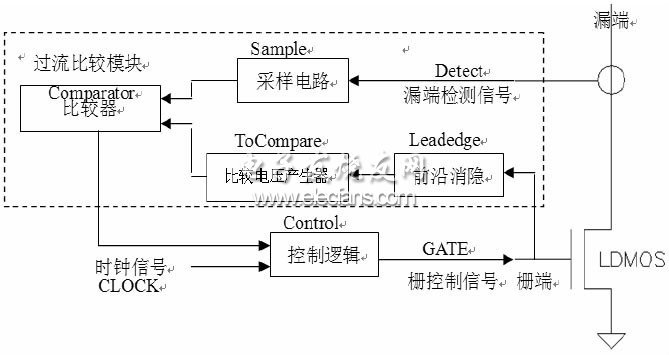

图2 是实现上述功能的电路框架图,由过流比较模块、控制逻辑等组成。

?

图2 过流保护电路框架

2 电路设计

2.1 过流比较模块

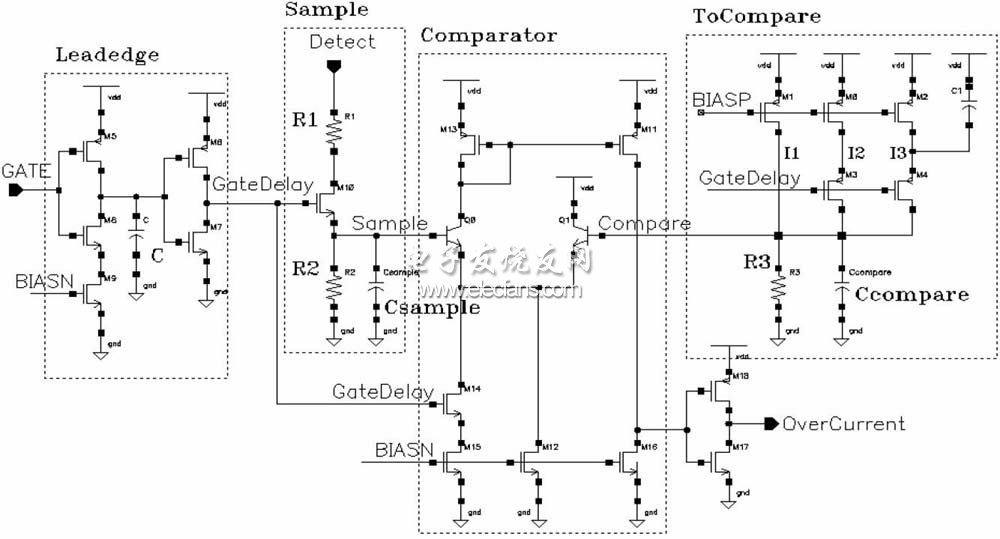

过流比较模块主要由前沿消隐Leadedge、采样电路Sample、比较电压产生器ToCompare 和过流比较器Comparator 等组成,如图3 所示。

前沿消隐电路由于存在片上寄生或外接电容和电感的影响,在LDMOS 管开启的瞬间,会在LDMOS 管漏极输出端出现尖峰电压,可能造成过流误判。必须增设前沿消隐电路,即对LDMOS 管栅控电压产生一个时间延迟,使在LDMOS 管开启的瞬间将过流比较器闭锁,等到尖峰通过后,再对LDMOS 管漏极信号进行采样测量和过流判断,从而消除漏电压尖峰的影响。如图3 所示,我们在其中加入一个偏置在固定电压V(BIASN)的NMOS 管,它相当于一个固定电流源,以限制电容放电的时间。

?

图3 过流比较模块电路图

合理设计相关的器件参数可以控制延迟时间的大小。

采样电路用开关控制电路实现对LDMOS 漏端的周期性电压采样,其中分压电路可采用大阻值有比电路结构。根据集成电路的特点,电阻比值的误差很容易被控制在1%范围之内。

当LDMOS 的栅电压V (GATE) 为高,即LDMOS 管导通时,使图3 中的采样开关管M10(具有较高耐压和较低导通电阻特性)也导通,同时开始采集LDMOS 管的饱和漏极电压;而当LDMOS 管的栅电压V(GATE)为低,即LDMOS 管关闭时(非过流现象),采样电路则不工作。