功率MOSFET常用于便携

和无线产品中,其应用

包括电池保护、负载管理和DC-DC转换等。对于这些应用,功率MOSFET最重要的特性便是其漏极-源极导通电阻Rds(on)。Rds(on)较小的功率MOSFET能够延长电池寿命,提高功率转化效率。同时,便携产品(如手机以及PDA等)的尺寸也在缩小,因此需要减小功率MOSFET的封装尺寸。近年来,为同时减小Rds(on)和封装尺寸,生产这些功率MOSFET的硅技术有了很大的改进,

功率MOSFET是典型的立式器件,漏极位于芯片的底部,源极和栅极位于上部表面。功率MOSFET经两次扩散过程制成,先进行一次体扩散(也称为“基极”扩散),然后进行源极扩散。为获得大沟道宽度,功率MOSFET的设计使用了大量并行连接的单元块。虽然每个单元的沟道宽度很小,并行连接数千个到数百万个单元,就能得到具有极大沟道宽度的晶体管了。由于MOSFET的Rds(on)与它的沟道宽度成反比,而载流容量与沟道宽度成正比,这样就制成了一个Rds(on)小且载流容量高的MOSFET。因此,功率MOSFET两个重要的设计特性便是其“单元密度”(定义为单位面积中的单元个数)以及“沟道密度”(定义为MOSFET中单位面积的沟道宽度)。

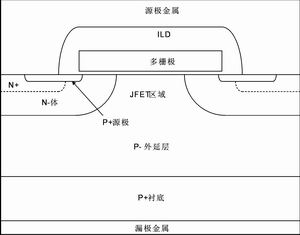

图1所示为功率MOSFET的一种,称为平面功率MOSFET。在平面功率MOSFET中,体扩散在公共漏极区域中形成盆状。电流从源极流出,经过硅上部表面形成的沟道,然后垂直流过漏极,到达晶片的底部。在这种结构中,相邻体扩散之间的间隔不能做的很小,因为这样会导致盆之间的JFET区域被夹断,致使Rds(on)增大。因此,平面功率MOSFET的单元密度受其沟道长度以及相邻体扩散之间间隔的限制。直到最近,市场上大多数功率MOSFET都是平面功率MOSFET。

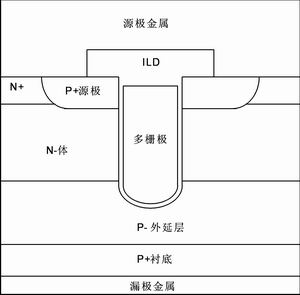

另一种类型的功率MOSFET为沟道功率MOSFET,如图2所示,这种MOSFET近几年已经越来越流行。与平面功率MOSFET不同,沟道MOSFET的沟道是在蚀刻于硅上的沟道边墙上垂直形成的。沟道从硅的上部表面穿过源极和体扩散,一直延伸到漏极区域。由于沟道是垂直形成的,在体扩散之间没有间隔限制,所以沟道MOSFET能够达到的沟道密度比平面功率MOSFET高得多。因此,对于给定的芯片尺寸,沟道功率MOSFET能够获得大大小于平面功率MOSFET的Rds(on)。这改善了Rds(on)的性能,然而由于过程变得复杂,成本较之平面功率MOSFET也有所提高。

近几年来,Rds(on)极小的沟道MOSFET已经面市,应用于诸如SO-8、TSSOP-8等的封装中。然而,由于近来便携和无线应用中的封装尺寸有越来越小的趋势,这些相对较大的封装正被TSOP-6、ChipFET(1)及SC-88等较小的封装所取代。由于能够放入这些小尺寸封装中的芯片尺寸也较小,这就增大了MOSFET的Rds(on)。因此,我们需要一种能形成较小Rds(on)的沟道技术。最近,安森美开发了一种创新的P沟道MOSFET技术,以便携和无线产品为应用目标。

图1 平面功率MOSFET的截面图

图2 沟道功率MOSFET的截面图

器件设计

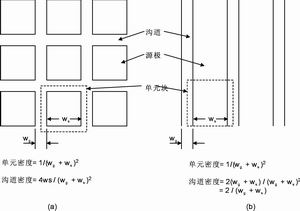

沟道功率MOSFET的设计可以使用闭合单元或条纹设计。在单元设计中,栅极在硅中形成一个栅格,包围了体区域和源极区域;而在条纹设计中,栅极设计为条纹状。现在市场上的沟道MOSFET使用了各种不同的布局,如方形单元、六边形单元和条纹等。选择哪种布局会影响沟道MOSFET的沟道密度,由此影响其Rds(on)。图3列出了最小单元间距相同的方形单元设计和条纹设计的沟道密度对比。可以看到,只要多栅极宽度wg小于源极区域的宽度ws,单元设计的沟道密度较高,因此Rds(on)也较小。

随着对更小的尺寸、更薄的栅极氧化物和更高的单元密度的需求不断增加,大多数MOSFET制造商在其最新的沟道产品中都转而使用了条纹设计。这是因为条纹设计避免了单元设计中固有的几个角,通常使栅极氧化物的质量更优,并且易于制造。但这种条纹设计有着减小沟道密度的不利影响,因而提高了Rds(on)。安森美半导体的沟道处理技术能够在制造中同时实现小尺寸的沟道MOSFET、薄栅极氧化物和高单元密度,在使用方形单元设计的同时保证栅极氧化物的质量和可制造性。使用方形单元设计,能够得到1.25mm/mm2的沟道密度,比其他MOSFET制造商的沟道密度高出约40%。

器件制造

这种新型MOSFET使用0.40mm光刻法制造。P沟道MOSFET的制造从外延晶片开始,包括重掺杂P型衬底上的一层轻掺杂P型硅。应适当选择轻掺杂P型外延层的电阻率和厚度,以获得器件要求的击穿电压。接下来,使用标准的半嵌入式LOCOS工序来定义器件的有效面积区,以及端子区域的生长域氧化物。接着将磷植入有效区域并发生扩散,形成N体区域。随后,一个用于确定沟道的硬掩模被沉积并形成图案,接着是沟道蚀刻。然后,生成一个牺牲氧化物,并进行蚀刻。牺牲氧化物的目的是使沟道的边角圆滑,并使硅表面因沟道蚀刻而造成的粗糙变得光滑。接着生成一层薄的栅极氧化物,再进行多晶硅栅极沉积和蚀刻。然后进行扩散工序,P+源极植入和N+体增强植入,形成与N体的连接。接点和金属是使用传统工序形成的。

图3 (a)单元设计;(b)条纹设计

性能

单元和条纹设计在相同的掩模上具有不同的最小间距(即不同的单元密度)。这样就能直接在同一晶片上比较不同的设计,消除了与工序或与初始材料相关的变化所引起的性能差异。

ChipFET封装式沟道MOSFET的特性表明,在栅极电压为4.5V的8V和20V P沟道器件中Rds(on)分别为19mW和21mW。这比原先相同封装的Rds(on)值低了约40%。在栅极电压较低(如2.5V和1.8V)时,也可实现类似的Rds(on)改进。

单元设计与在同一晶片上制造的条纹设计相比,栅极到源极的漏泄、漏极到源极的漏泄、击穿电压和阈值电压都没有明显的差异。栅极击穿试验显示两种设计的栅极氧化物的击穿场强约为10mV/cm,说明方形单元的设计并没有影响栅极氧化物的质量。

将单元设计的Rds(on)与具有相同间距(即相同的单元密度)的条纹设计相比,发现单元设计的Rds(on)比条纹设计小。这是我们可以预料到的,因为虽然单元密度相同,但条纹设计的沟道密度比单元设计低。这表示要获得与单元设计相同的Rds(on),条纹设计必须具有比单元设计更高的单元密度(即器件尺寸更小)。