对反激同步整流在低压小电流DC-DC变换器中的应用进行了研究,介绍了主电路工作原理,几种驱动方式及其优缺点,选择出适合于自驱动同步整流的反激电路拓扑,并通过样机试验,验证了该电路的实用性。

引言

低压大电流DC-DC模块电源一直占模块电源市场需求的一半左右,对其相关技术的研究有着重要的应用价值。模块电源的高效率是各厂家产品的亮点,也是业界追逐的重要目标之一。同步整流可有效减少整流损耗,与适当的电路拓扑结合,可得到低成本的高效率变换器。本文针对36V-75V输入,3.3V/15A输出的二次电源模块,在分析同步整流技术的基础上,根据同步整流的特点,选择出适合于自驱动同步整流的反激电路拓扑,进行了详细的电路分析和试验。

反激同步整流

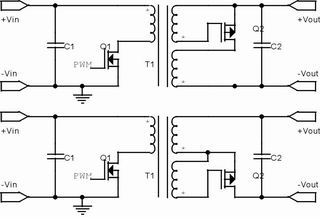

基本的反激电路结构如图1。

其工作原理:主MOSFET Q1导通时,进行电能储存,这时可把变压器看成一个电感,原边绕组电流Ip上升斜率由dIp/dt=Vs/Lp决定,磁芯不饱和,则Ip 线性增加;磁芯内的磁感应强度将从Br增加到工作峰值Bm;Q1关断时,原边电流将降到零,副边整流管开通,感生电流将出现在副边;按功率恒定原则,副边安匝值与原边安匝值相等。

在稳态时,开关导通期间,变压器内磁通增量△Φ应等于反激期间内的磁通变化量,即:

△Φ=VsTon / Np=Vs’Toff / Ns

从此式可见,如果磁通增量相等的工作点稳定建立时,变压器原边绕组每匝的伏-秒值必然等于副边每匝绕组的伏-秒值。

反激变换器的拓扑实际就是一个BUCK-BOOST组合的变换器拓扑的应用,而且如果副边采用同步整流,电路总是工作于CCM的模式下,其电压增益

M=Vo/Vs=K·D/(1-D)(K为原副边匝数比)

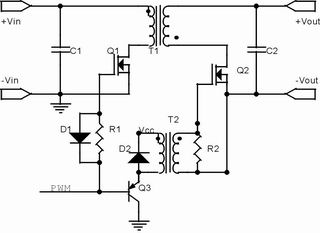

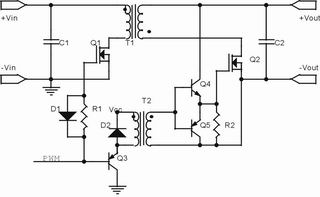

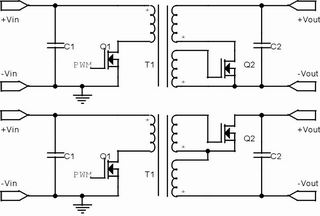

用PMOSFET和MOSFET替代图1中的萧特基二极管,可以实现同步整流的4种电路结构如图2和图3

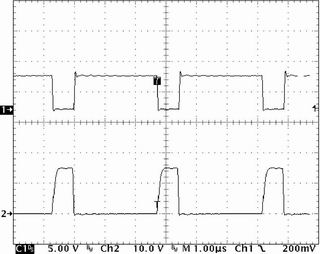

反激电路的开关电压波形见图4,是标准的矩形波,非常适合同步整流驱动。设计的关键点在于同步整流管的位置与驱动电路的结构配合、波形的整形限幅和死区控制。

图1 基本反激电路结构图

图2 由NMOSFET构成的反激同步整流电路结构

图3 由PMOSFET构成的反激同步整流电路结构

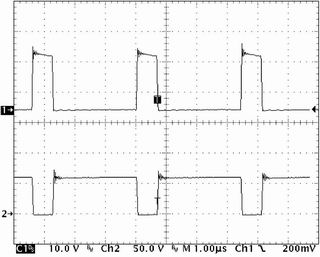

图4 CH1-整流管实验波形/ CH2-主开关实验波形

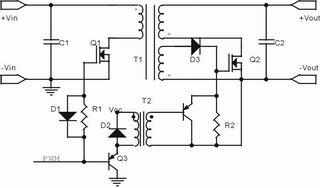

图5 一种实际的外驱电路

图6 增加驱动能力的外驱电路

图7 由NMOSFET构成的反激同步整流自驱动电路结构

图8 由PMOSFET构成的反激同步整流自驱动电路结构

图9 反激同步整流半自驱电路结构

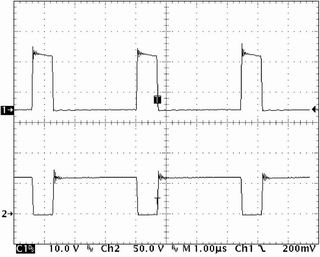

图10、Vgs驱动波形,CH1同步整流管,CH2主开关管

图11、Vds波形,CH1同步整流管,CH2主开关管

图12 转换效率曲线

反激同步整流驱动电路选择

同步整流管的驱动方式有三种:第一种是外加驱动控制电路,优点是其驱动波形的质量高,调试方便。缺点是:电路复杂,成本高,在追求小型化和低成本的今天只有研究价值,基本没有应用价值。图5是简单的外驱电路,R1D1用于调整死区。该电路的驱动能力较小,在同步整流管的Ciss较小时,可以使用。图6是在图5的基础上增加副边推挽驱动电路的结构,可以驱动Ciss较大的MOSFET。在输出电压低于5V时,需要增加驱动电路供电电源。

第二种是自驱动同步整流。优点是直接由变压器副边绕组驱动或在主变压器上加独立驱动绕组,电路简单、成本低和自适应驱动是主要优势,在商业化产品中广泛使用。缺点是电路调试的柔性较少,在宽输入低压范围时,有些波形需要附加限幅整形电路才能满足驱动要求。图7和图8是四种反激同步整流的电路结构。由于Vgs的正向驱动都正比于输出电压,调节驱动绕组的匝数可以确定比例系数,且输出电压都是很稳定的,所以驱动电压也很稳定。比较麻烦的是负向电压可能会超标,需要在设计变压器变比时考虑驱动负压幅度。

第三种是半自驱。其驱动波形的上升或下降沿,一个是由主变压器提供的信号,另一个是独立的外驱动电路提供的信号。图9是针对自驱的负压问题,用单独的放电回路,提供同步整流管的关断信号,避开了自驱动负压放电的电压超标问题。

实验结果

根据图7电路,设计了一台15W样机,输入电压36-75V,输出5V/3A,体积50mm/25mm/8.5mm。开关频率300kHz,磁心选用国产FEY12.5,变压器匝比3:1,磁心中柱气隙0.2mm。

同步整流管选择的主要依据是:整流管导通电阻尽量小,电压和电流不超过整流管的电压和电流限值,这里选用Motorola公司的MTB75N05HD( Vds=50V,Rds=7mΩ)

同步整流管的驱动波形如图10,为标准的矩形波。

实测的效率曲线如下,低压满载时在87%以上。与萧特基二极管整流的典型效率82%相比,模块损耗减少了30%。

结语

理论分析和样机验证,证明反激同步整流的的效率在低压输出条件下有明显的优势,模块本身的功耗比萧特基整流低30%,可以提高30%的模块功率密度,具有极大的推广和应用价值。