实现补码加减运算的逻辑电路

运算前,X、Y寄存器分别存储被加(减)数 和 加(减)数,计算结果存回X寄存器;F为加法器,能在命令X→F和Y→F信号的控制下接收两个寄存器中的数据并完成加法运算,运算结果在F→X命令信号的控制下接收回X寄存器中。

为实现减运算,应将Y寄存器中补码数据的负数表示送到加法器F,这可以通过送Y寄存器中每位数据的反码并在F的最低位给出进位1输入信号变通完成,用/Y→F和1→F控制命令实现。

相关热词:#补码

短路开关工作原理

短路开关工作原理

时间:2026-03-07

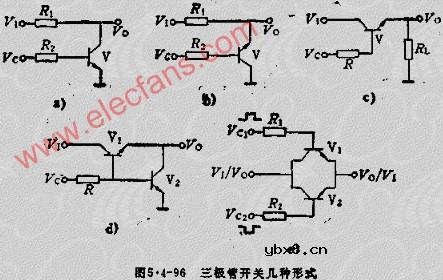

场效应晶体管开关电路

场效应晶体管开关电路

时间:2026-03-07

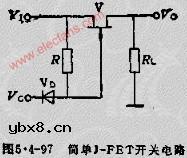

J-FET开关电路工作原理

J-FET开关电路工作原理

时间:2026-03-07

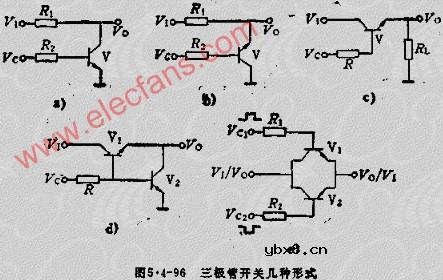

MOS-FET开关电路

MOS-FET开关电路

时间:2026-03-07

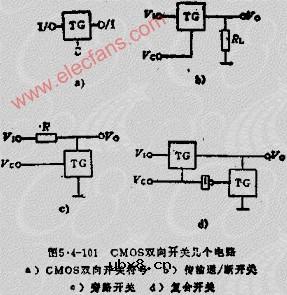

CMOS双向开关工作原理

CMOS双向开关工作原理

时间:2026-03-07

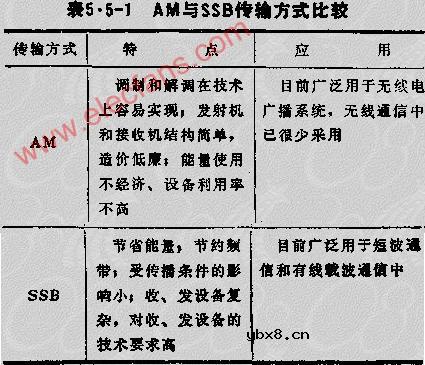

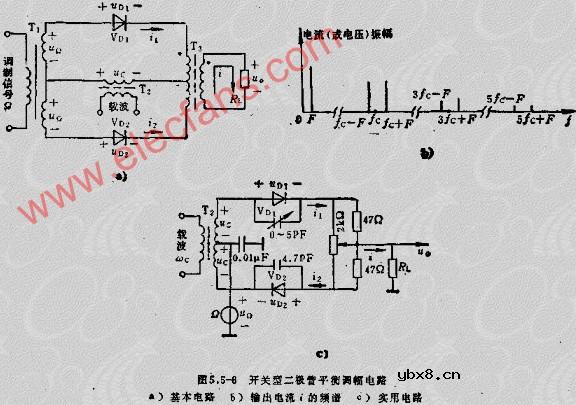

振幅调制的传输方式

振幅调制的传输方式

时间:2026-03-07

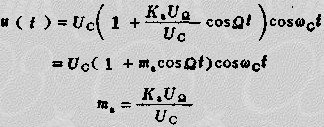

调幅信号的性质

调幅信号的性质

时间:2026-03-07

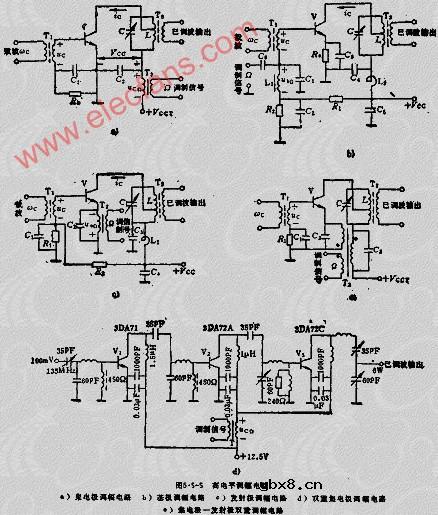

调幅电路工作原理--高电平调幅电路

调幅电路工作原理--高电平调幅电路

时间:2026-03-07

调幅电路工作原理--低电平调幅电路

调幅电路工作原理--低电平调幅电路

时间:2026-03-07

检波的基本概念

检波的基本概念

时间:2026-03-07

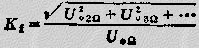

彩灯电路

彩灯电路

时间:2026-03-05

三相异步电动机原理

三相异步电动机原理

时间:2026-03-04

三相异步电动机的七种调速方式

三相异步电动机的七种调速方式

时间:2026-03-04

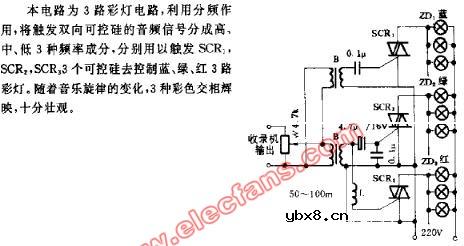

转角测量电路

转角测量电路

时间:2026-03-05

经典的正弦波发生电路

经典的正弦波发生电路

时间:2026-03-05

电度表的工作原理

电度表的工作原理

时间:2026-03-04

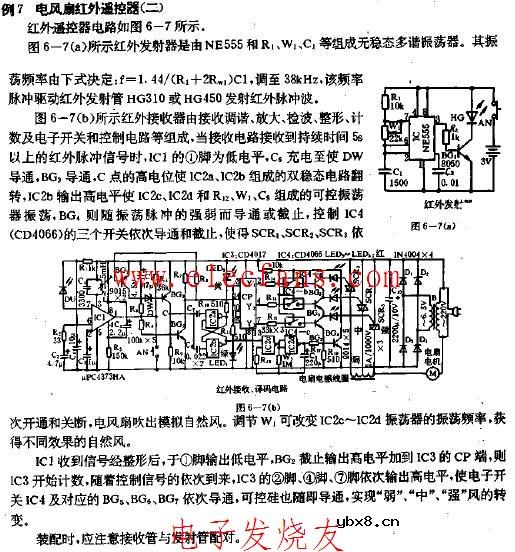

电风扇红外遥控器2

电风扇红外遥控器2

时间:2026-03-04

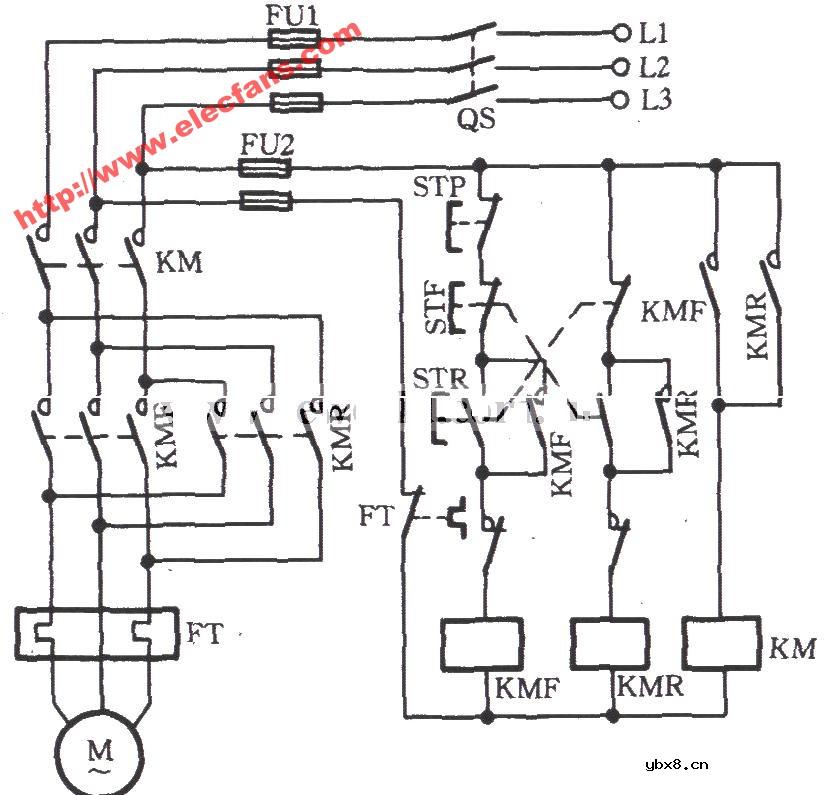

电动机单线远程正反转控制电路图

电动机单线远程正反转控制电路图

时间:2026-03-04

三相异步电动机的拆装详讲

三相异步电动机的拆装详讲

时间:2026-03-04

USB转232电路图

USB转232电路图

时间:2026-03-04