对于功率转换器,寄生参数最小的热回路PCB布局能够改善能效比,降低电压振铃,并减少电磁干扰(EMI)。本文讨论如何通过最小化PCB的等效串联电阻(ESR)和等效串联电感(ESL)来优化热回路布局设计。本文研究并比较了影响因素,包括解耦电容位置、功率FET尺寸和位置以及过孔布置。通过实验验证了分析结果,并总结了最小化PCB ESR和ESL的有效方法。

热回路和PCB布局寄生参数

开关模式功率转换器的热回路是指由高频(HF)电容和相邻功率FET形成的临界高频交流电流回路。它是功率级PCB布局的最关键部分,因为它包含高dv/dt和di/dt噪声成分。设计不佳的热回路布局会产生较大的PCB寄生参数,包括ESL、ESR和等效并联电容(EPC),这些参数对功率转换器的效率、开关性能和EMI性能有重大影响。

图1显示了同步降压DC-DC转换器原理图。热回路由MOSFET M1和M2以及解耦电容CIN形成。M1和M2的开关动作会产生高频di/dt和dv/dt噪声。CIN提供了一个低阻抗路径来旁路高频噪声成分。然而,器件封装内和热回路PCB走线上存在寄生阻抗(ESR、ESL)。高di/dt噪声通过ESL会引起高频振铃,进而导致EMI。ESL中存储的能量在ESR上耗散,导致额外的功率损耗。因此,应尽量减小热回路PCB的ESR和ESL,以减少高频振铃并提高效率。 准确提取热回路的ESR和ESL,有助于预测开关性能并改进热回路设计。器件的封装和PCB走线均会影响回路的总寄生参数。本文主要关注PCB布局设计。有一些工具可帮助用户提取PCB寄生参数,例如Ansys Q3D、FastHenry/FastCap、StarRC等。Ansys Q3D之类的商用工具可提供准确的仿真,但通常价格昂贵。FastHenry/FastCap是一款基于部分元件等效电路(PEEC)数值建模的免费工具,可以通过编程提供灵活的仿真来探索不同的版图设计,但需要额外的编程。FastHenry/FastCap寄生参数提取的有效性和准确性已经过验证,并与Ansys Q3D进行了比较,结果一致。在本文中,FastHenry用作提取PCB ESR和ESL的经济高效的工具。

图1.带热回路ESR和ESL的降压转换器

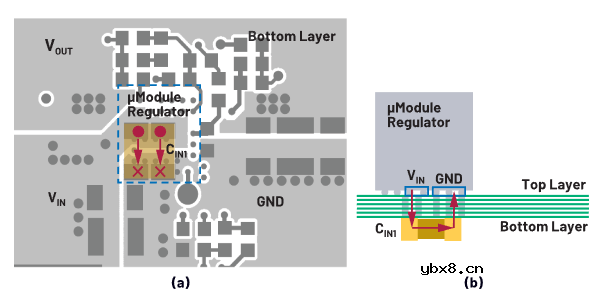

图2.垂直热回路1:(a)俯视图和(b)侧视图

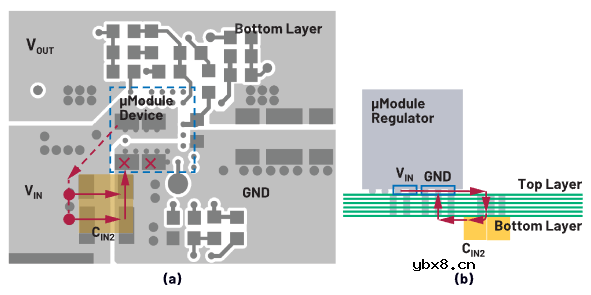

图3.垂直热回路2:(a)俯视图和(b)侧视图

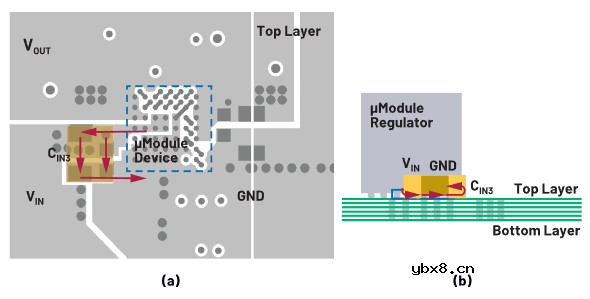

图4.水平热回路:(a)俯视图和(b)侧视图

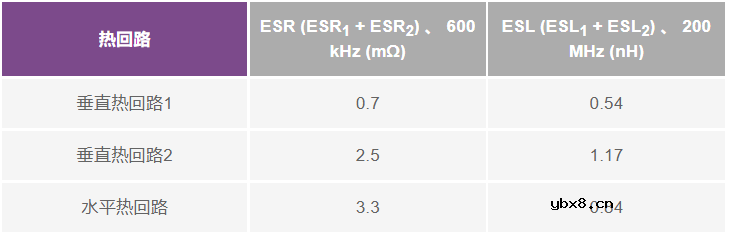

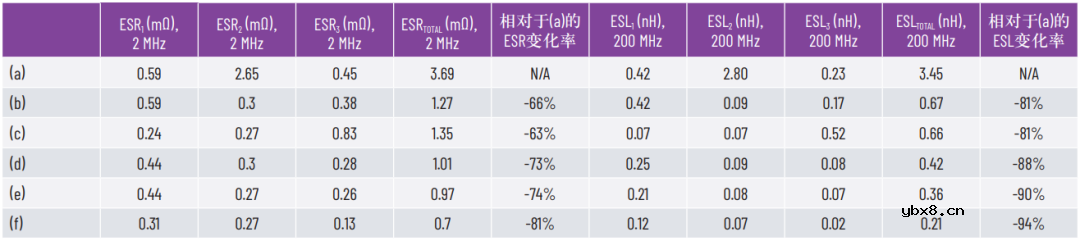

表1.使用FastHenry提取的不同热回路的PCB ESR和ESL

为了通过实验验证不同热回路的ESR和ESL,我们测试了12V转1V CCM运行时演示板的效率和VIN交流纹波。理论上,ESR越低,则效率越高,而ESL越小,则VSW振铃频率越高,VIN纹波幅度越低。图5a显示了实测效率。垂直热回路1的效率最高,因为其ESR最低。水平热回路和垂直热回路1之间的损耗差异也是基于提取的ESR计算的,这与图5b所示的测试结果一致。图5c中的VINHF纹波波形是在CIN上测试的。水平热回路具有更高的VIN纹波幅度和更低的振铃频率,因此验证了其回路ESL高于垂直热回路1。另外,由于回路ESR更高,因此水平热回路的VIN纹波衰减速度快于垂直热回路1。此外,较低的VIN纹波降低了EMI,因而可以使用较小的EMI滤波器。

图5.演示板测试结果:(a)效率,(b)水平回路与垂直回路1之间的损耗差异,(c)15A输出时M1导通期间的VIN纹波

表2.对于不同器件形状和位置,使用FastHenry提取的热回路PCB ESR和ESL

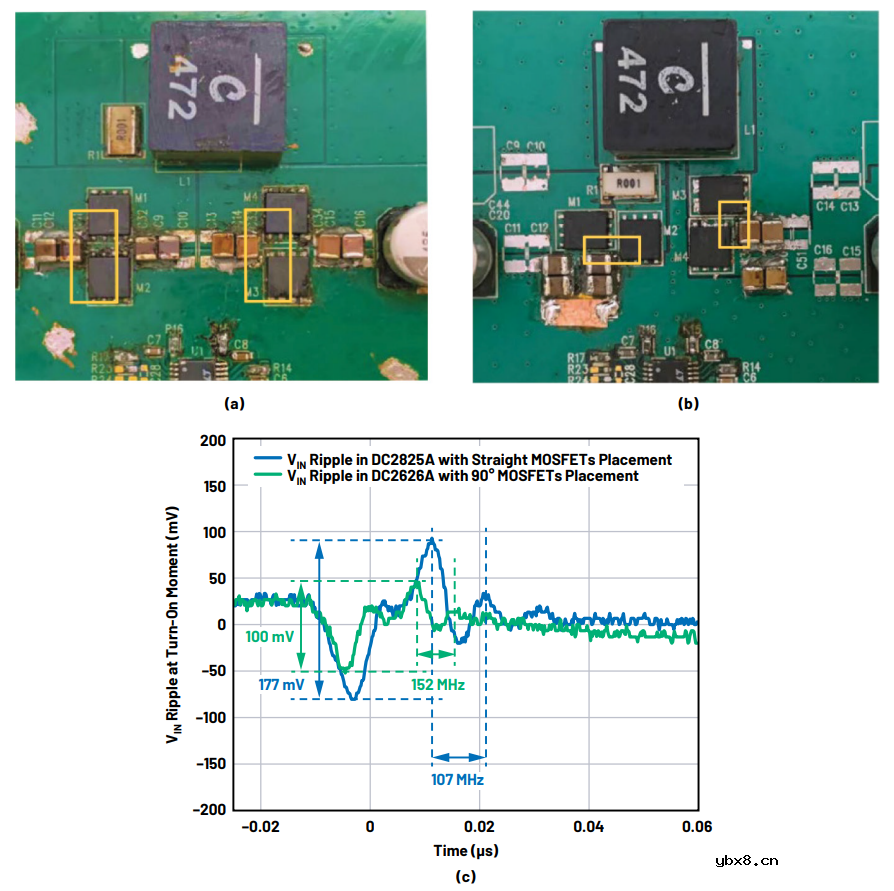

为了通过实验验证MOSFET布置的影响,我们使用了ADI公司的高效率4开关同步降压-升压控制器演示板LT8390/DC2825A和LT8392/DC2626A。如图 7a和图7b所示,DC2825A采用直线MOSFET布置,DC2626A采用90°形状的MOSFET布置。为了进行公平比较,两个演示板配置了相同的MOSFET和解耦电容,并在36V转12V/10A、300 kHz降压操作下进行了测试。图7c显示了M1导通时刻测得的VIN交流纹波。采用90°形状的MOSFET布置时,VIN纹波的幅度更低,谐振频率更高,这就验证了热回路路径较短导致PCB ESL更小。相反,直线MOSFET布置的热回路更长,ESL更高,导致VIN纹波幅度要高得多,并且谐振频率更低。根据Cho和Szokusha研究的EMI测试结果,较高的输入电压纹波还会导致EMI辐射更严重。

图6.热回路PCB模型:(a)5mm×6mm MOSFET,直线布置;(b)5mm×6mm MOSFET,以90°形状布置;(c)5mm×6mm MOSFET,以180°形状布置;(d)两个并联的3.3mm×3.3mm MOSFET,以90°形状布置;(e)两个并联的3.3mm×3.3mm MOSFET,以90°形状布置,带有接地层;(f)对称的3.3mm×3.3mm MOSFET,位于顶层和底层,以90°形状布置。

图7.(a) LT8390/DC2825A热回路,MOSFET以直线布置;(b) LT8392/DC2626A热回路,MOSFET以90°形状布置;(c) M1导通时的VIN纹波波形。

图8.热回路PCB模型,(a) 5个GND过孔靠近CIN和M2布置;(b) 14个GND过孔布置在CIN和M2之间;(c) 基于(b),GND上再布置6个过孔;(d) 基于(c),GND区域上再布置9个过孔。

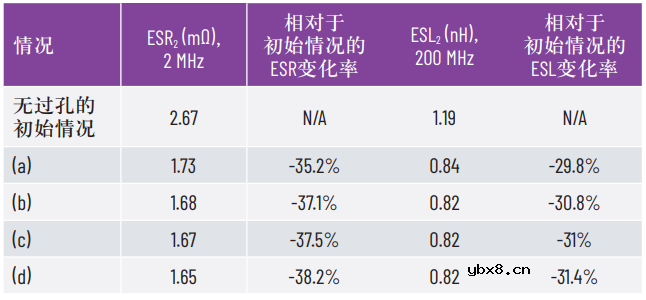

热回路中的过孔布局对回路ESR和ESL也有重要影响。图8对使用两层PCB结构和直线布置功率FET的热回路进行了建模。FET放置在顶层,第二层是接地层。CINGND焊盘和M2源极焊盘之间的寄生阻抗Z2是热回路的一部分,作为示例进行研究。Z2是从FastHenry提取的。表3总结并比较了不同过孔布置的仿真ESR2和ESL2。

通常,添加更多过孔会降低PCB寄生阻抗。然而,ESR2和ESL2的降低程度与过孔数量并不是线性比例关系。靠近引脚焊盘的过孔,所导致的PCB ESR和ESL的降低最明显。因此,对于热回路布局设计,必须将几个关键过孔布置在靠近CIN和MOSFET焊盘的位置,以使高频回路阻抗最小。

表3.使用不同过孔布置时提取的热回路PCB ESR2和ESL2

结论减小热回路的寄生参数有助于提高电源效率,降低电压振铃,并减少EMI。为了尽量减小PCB寄生参数,我们研究并比较了使用不同解耦电容位置、MOSFET尺寸和位置以及过孔布置的热回路布局设计。更短的热回路路径、更小尺寸的MOSFET、对称的90°形状和180°形状MOSFET布置、靠近关键元器件的过孔,均有助于实现最低的热回路PCB ESR和ESL。

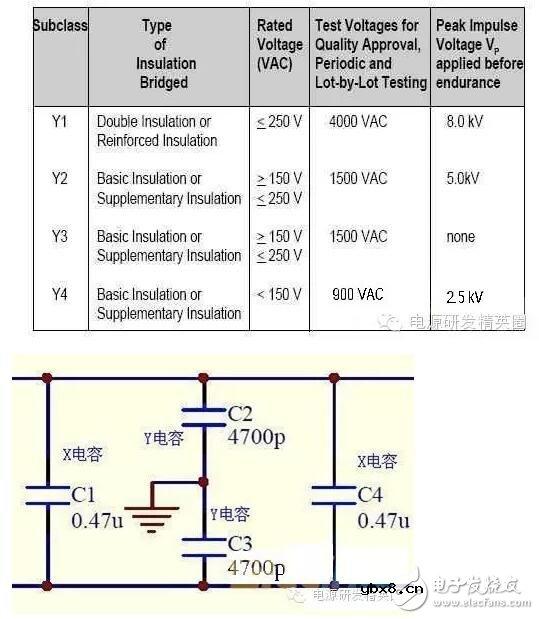

详解X/Y安规电容作用及安全等级

详解X/Y安规电容作用及安全等级

时间:2026-03-05

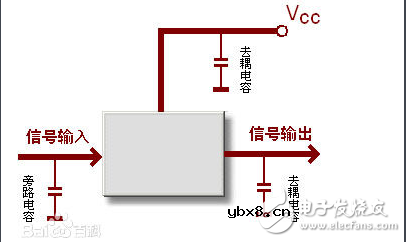

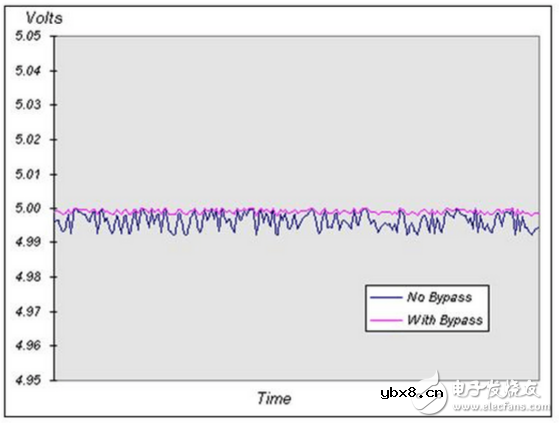

去耦电容和bypass电容、滤波电容的原理和区...

去耦电容和bypass电容、滤波电容的原理和区...

时间:2026-03-05

信号电路与电源电路中去耦电容、旁路电容、...

信号电路与电源电路中去耦电容、旁路电容、...

时间:2026-03-05

旁路电容的作用与应用原理详解

旁路电容的作用与应用原理详解

时间:2026-03-05

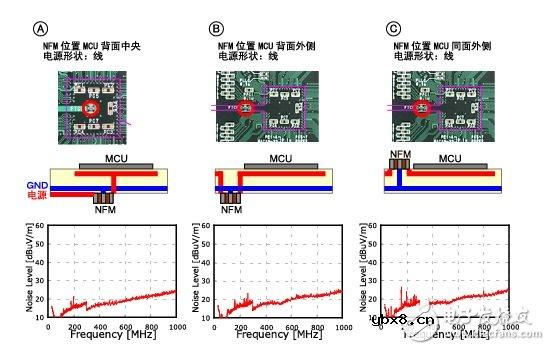

片状三端子电容器的注意事项及使用技巧

片状三端子电容器的注意事项及使用技巧

时间:2026-03-05

瓷片电容104是多大 瓷片电容104耐压值是多少

瓷片电容104是多大 瓷片电容104耐压值是多少

时间:2026-03-05

详细瓷片电容规格/分类

详细瓷片电容规格/分类

时间:2026-03-05

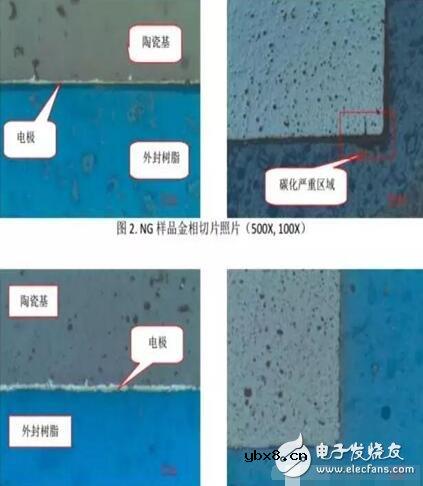

陶瓷电容耐压不良失效分析及常见七大失效原...

陶瓷电容耐压不良失效分析及常见七大失效原...

时间:2026-03-05

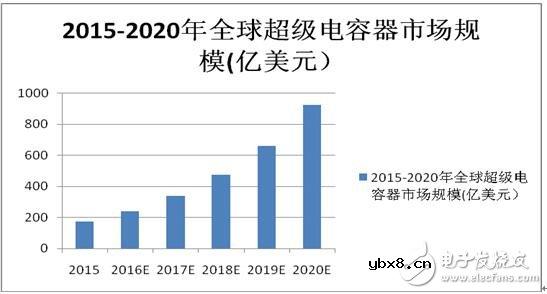

中国超级电容器市场达100亿元

中国超级电容器市场达100亿元

时间:2026-03-05

MLCC高容物料急剧短缺,跟三星note7爆炸案有...

MLCC高容物料急剧短缺,跟三星note7爆炸案有...

时间:2026-03-05

玻璃釉电容器的结构与特点

玻璃釉电容器的结构与特点

时间:2026-03-05

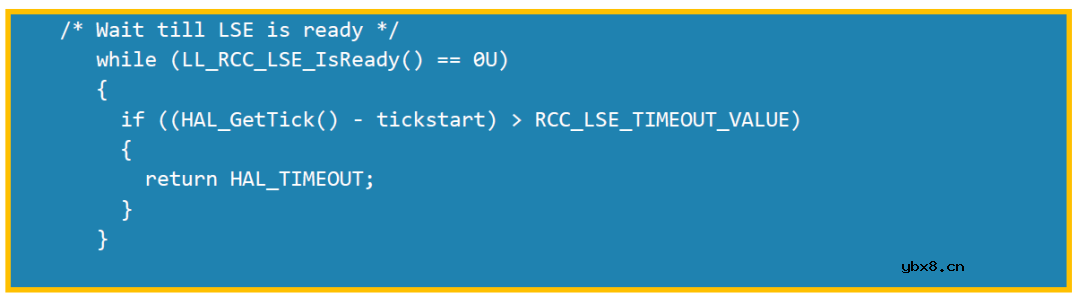

关于STM32WL LSE 添加反馈电阻后无法起振的...

关于STM32WL LSE 添加反馈电阻后无法起振的...

时间:2026-03-05

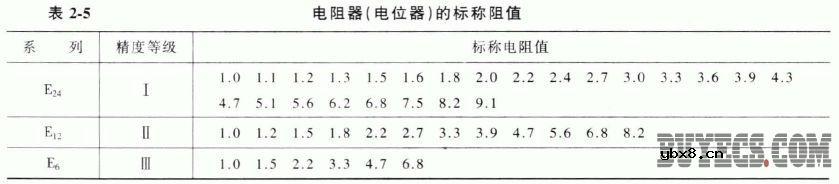

电阻的标称阻值和允许偏差

电阻的标称阻值和允许偏差

时间:2026-03-05

聚四氟乙烯电容器的结构与特点

聚四氟乙烯电容器的结构与特点

时间:2026-03-05

漆膜电容器的结构与特点

漆膜电容器的结构与特点

时间:2026-03-05

复合介质电容器的结构与特点

复合介质电容器的结构与特点

时间:2026-03-05

瓷介电容器的结构与特点

瓷介电容器的结构与特点

时间:2026-03-05

电解电容器的结构与特点

电解电容器的结构与特点

时间:2026-03-05

电解电容的型号

电解电容的型号

时间:2026-03-05

铝电解电容特性型号参数表

铝电解电容特性型号参数表

时间:2026-03-05