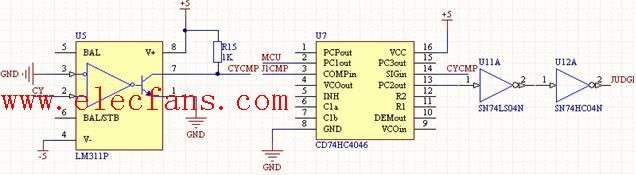

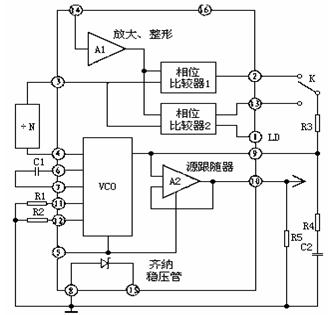

过零比较和锁相环相位比较器电路原理图如图

?

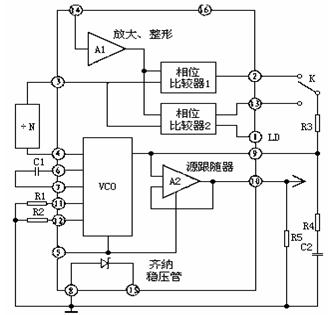

现在常使用集成电路的锁相环CD4046,是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约

?

1脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。2脚相位比较器Ⅰ的输出端。3脚比较信号输入端。13脚相位比较器Ⅱ的输出端。14脚信号输入端。对相位比较器Ⅱ而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“

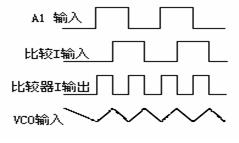

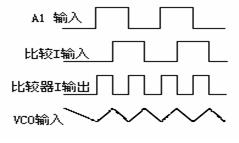

图2.13?? 比较器输出波形图

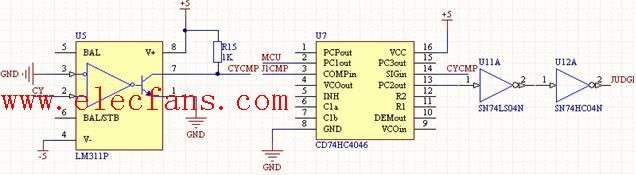

过零比较和锁相环相位比较器电路原理图如图

?

现在常使用集成电路的锁相环CD4046,是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约

?

1脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。2脚相位比较器Ⅰ的输出端。3脚比较信号输入端。13脚相位比较器Ⅱ的输出端。14脚信号输入端。对相位比较器Ⅱ而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“

图2.13?? 比较器输出波形图