本文介绍的AD9956就是一种高集成度的高性能DDS芯片,它可产生高分辨率、高扫描率、可编程的信号,可广泛地应用于雷达信号源中。

1 AD9956的主要特点参数

AD9956可产生μHz频率分辨率、精微电流消耗的高分辨率、可编程信号源,并可根据需要配置成多种电路,因而可用于雷达和扫描系统中FM啁啾声信号的生成、汽车雷达、测试和测量设备以及声光设备驱动器之中。

AD9956的主要性能指标如下:

●具有400MSPS内部DDS时钟速率;

●带14位DAC和48位频率调谐字;

●带有200MHz输入的相位检测器;

●可进行电荷泵电流的数字控制;

●可对650MHz PECL驱动器的转换速率进行编程控制;

●1kHz失调时的相位噪音小于135dBc/Hz;

●160MHz时的SFDR为80dB;

●可进行25MBps写速度串行I/O控制;

●带有可编程?1~16 相位检测器和50MHz预标定器(÷M,÷N);

●内含可编程的RF预标定器(÷R)(R=2,4,8);

●工作电压为1.8V;

●I/O和电荷泵电源电压为3.3V;

●可用软件控制功耗;

●采用48引脚MLF封装。

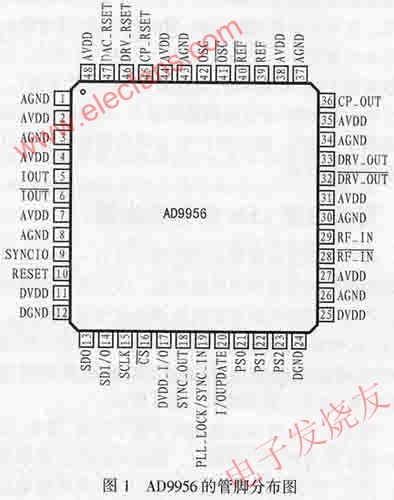

2 管脚分布

AD9956引脚排列如图1所示。该器件的主要引脚包括串口复位信号(SYNC_I/O)、I/O更新信号(I/O UPDATE)、RF预标定器和DDS参考时钟输入(RF_IN)、

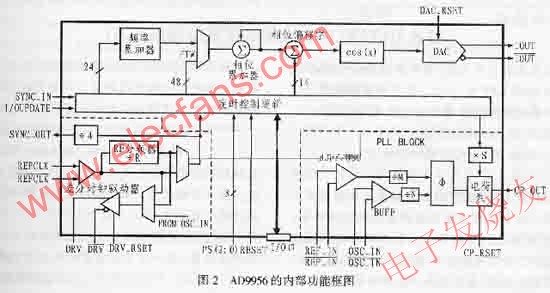

3 结构原理

AD9956的功能框图如图2所示。AD9956内部由DDS核、RF分频DAC、鉴相器/电荷泵和一个差分时钟驱动器组成。其工作特性包括精确调谐的48-bit相位累加器、可提供匹配系统时延的14-bit相位偏移字以及可提供线性扫频的24-bit频率累加器。储存在相位累加器中的瞬时值可表示正弦频率的瞬时相位。在每个系统时钟周期,相位累加器的增量由储存在控制寄存器中的频率调谐字(FTW)决定,它一般通过FTW增加其值?直到溢出(超出最大值)。由于较大的FTW会引起频繁的溢出,因此可表示更高的频率。相反,较小的FTW会导致较慢的溢出以表示较低的频率。

4 高线性度LFM信号发生器

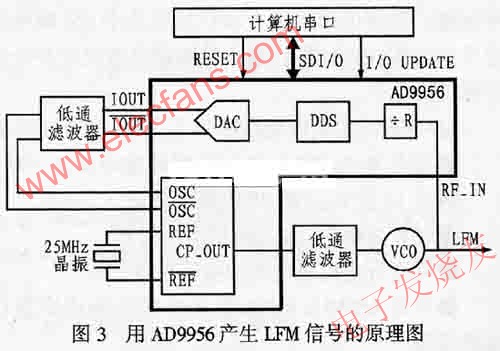

线性调频连续波雷达的距离分辨力一般可由线性调频信号的带宽和线性度决定。因此在雷达应用中,产生高线性度的宽带线性调频信号至关重要。由于AD9956的调谐分辨率达10μHz。所以利用AD9956可产生高线性度的宽带线性调频连续波(LFMCW)信号。其原理图如图3所示。

传统的PLL电路会遇到两个基本限制:首先,反馈环路上的分频器是整数值,因此环路的分辨率受限。其次,简单的分频器用在环路上时,其环路增益是静态的,这一点限制了输出频率的扫描。而AD9956把DDS部分用在了PLL环路上,这样就克服了传统PLL的两个限制。

图3中的DDS线性扫频输出的信号经DAC转变为模拟信号后,再通过低通滤波器输入鉴相器的OSC和OSC端,鉴相器输出CP_OUT通过低通滤波器后作为VCO输入,最后再将VCO输出经过R分频器后输入到DDS的输入端。

该设计中的DDS扫频起始频率为24MHz,终止频率为25MHz,最高分辨率达10μHz。VCO扫频起始频率为2.6GHz,终止频率为2.7GHz分辨率达0.01μHz。

通过编程可以改变扫频速率及分辨率,同时可以改变输出频率。AD9956控制字的改变可通过计算机串口实现。其主过程为:首先是主复位RESET ,主要任务是清除所有的累加器并使所有的寄存器恢复为默认值;其次是送串口数据?SDI/O ,其中3-线方式只做输入,2-线方式则既做输入也做输出;第三是更新串口(I/O UPDATE),即把所有I/O缓冲器里的数据送到各自对应的寄存器中,以实现对扫频速率、分辨率及输出频率的编程。