矩阵式变换器设计中的干扰抑制技术

1 概述

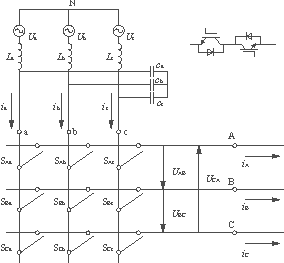

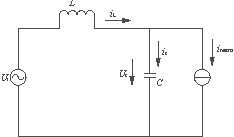

矩阵式变换器是一种强迫换相的交-交变换器,它由9个可控的双向开关,利用PWM控制将交流供电电源直接变换成负载所需的变压变频电源,其结构如图1所示。双向开关使用两个IGBT共集电极反向串联,利用器件内部的续流二极管以阻挡反向电压,结构紧凑,方便简单,开关损耗也较低。输入侧的L-C滤波器可有效减少输入电流的开关频率谐波。

图1 矩阵式变换器的原理性结构图

2 EMI分析

矩阵式变换器是AC/AC直接变换,电网和负载会相互直接影响,电网的波动会直接对负载(如异步电机)产生干扰;用IGBT和反并联二极管构成的双向开关,以及它们的控制电路DSP和CPLD等高速集成电路,都存在着高的di/dt,它们通过线路或元器件的引线电感引起瞬态电磁噪声,其频率为几千Hz,成为不可忽略的噪声源;PWM调制技术在各种电力电子装置中的广泛应用,在它们的主功率电路中,通常会流过一系列的PWM功率脉冲,其重复频率视应用场合可达几千Hz,因而这些脉冲电流中所包含的谐波可以达到几MHz乃至几十MHz的范围,而且它们产生的电磁噪声强度很大;而周围的设备和装置也会辐射电磁波,它们也成为不可忽视的干扰源。这些干扰源通过传导和辐射等方式对输出和输入电流、电压产生影响,必须想办法将其抑制或减少在可以接受的范围之内。

世界各国对电气设备的电磁兼容性均制定了相应的标准,特别是西欧,从1996年1月开始已强制严格执行其标准,我国也有相应的标准和法规,因此,必须采用输入滤波器减少矩阵式变换器产生的开关频率谐波,本文重点介绍输入滤波器的设计。

3 减少开关过程干扰

为了保证开关之间的安全切换,同一相输出的任意两组开关不能同时导通,否则将造成输入两相短路而产生电流峰值;三相开关也不能同时断开,否则就造成感性负载开路而感应高电压。但实际所采用的半导体开关器件IGBT不可能达到理想的瞬时导通和关断,在即将关断的器件退出导通之前,即将导通的器件不能达到理想状况的瞬时导通状态,换流时无法避免短暂的开通重叠或关断死区,因此,为了减少开关过程的干扰,安全的换流通常不能一步完成。

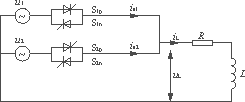

四步安全换流的思想是尽量减少短路和开路的危险开关状态。从开关S1到开关S2换流过程如图2所示。

图2 同一相负载两组开关的换流示意图

当iL>0时,四步开关顺序是:关S1n,开S2p,关S1p,开S2n。

当iL<0时,四步开关顺序是:关S1p,开S2n,关S1n,开S2p。

可见,四步换流成功地构成了对两个双向开关的换向控制,既阻止了可能使电源发生短路的开关组合,又保证了在任意时刻给负载提供至少一条流通路径,而且即将关断的器件被即将开通的器件施以反压时可以实现零电流开关,因此,采用四步换流方案可以减少50%的平均开关损耗。

优化开关顺序是将开关顺序设置为S1,S2,S3,S0,S3,S2,S1,即采用半对称PWM开关顺序,采用优化后的开关顺序可以减少33%的平均开关损耗。

4 输入滤波器设计

4.1 开关频率谐波

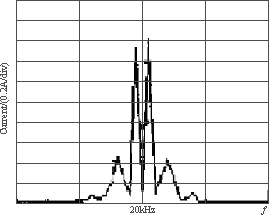

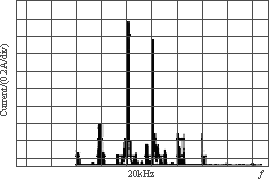

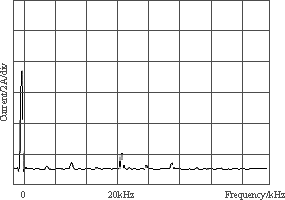

利用仿真和实验的方法可以得到三相输入电流的频谱,可以比较仿真和实验波形中开关频率及其谐波的峰值及其位置,并以此作为滤波器设计的依据。

利用Matlab仿真的输出频率为30Hz的输入电流频谱如图3所示。图4是实际的开关频率为20kHz,功率为3.5kW的矩阵式变换器的未滤波的输入电流频谱。可见,在仿真和实验波形之间有很多相关性,它们在开关频率附近谐波成分很大。

图3 仿真得到的输入电流开关频率附近频谱

图4 实验得到的输入电流开关频率附近频谱

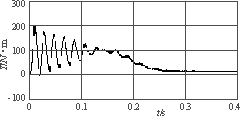

在矩阵式变换器驱动感应电机的系统中,电机启动过程的电磁转矩波形如图5所示。由图5可知,感应电机启动时转矩最大,由此产生的干扰电压也最大。知道了干扰电压的频谱,可以开始设计满足要求的输入滤波器了。

图5 电机启动过程电磁转矩波形图

图6 矩阵式变换器输入滤波器等效电路图

4.2 设计方法

可以采用多相LC滤波电路或带谐波选择的单相LC滤波器,但显然增加了系统的复杂性。本实验采用单相的LC滤波电路来满足设计要求。

输入滤波器的设计必须满足截止频率低于开关频率,体积和重量应尽可能小,在滤波电感上的压降应尽可能小,功率因数应尽可能大。为了减少对电网的干扰,矩阵式变换器要尽可能保证接近1的功率因数,因此,矩阵式变换器必须尽可能补偿由引入输入滤波器的延迟,因为电容是造成延迟的主要因素,所以输入电流比输入电压有一个延迟角。为了确保空间矢量调制策略的正确执行,我们设定π/6为最大的可以接受的延迟角。

输入滤波器设计根据图6所示,矩阵式变换器看成是一个电流源,为了得到功率因数为1,必须尽可能确保输入电流iL和输入电压Ui同相。

由图6可得

Uc=Ui-jωLiL=![]() (1)

(1)

imatrix=iL-jωCUc=iL-jωC(Ui-jωLiL)

=iL-ω2LCiL-jωCUi=iL(1-ω2LC)-jωCUi=![]() (2)

(2)

矩阵式变换器的延迟角(电流落后)限制为π/6,则

-arctan![]() +arctan

+arctan![]() <

<![]() (3)

(3)

由式(3)可得

C<![]() iL(4)

iL(4)

式中:ωc=![]() 为滤波器截止角频率。

为滤波器截止角频率。

滤波器电感引起的电压延迟可以忽略[5],滤波器的截止频率比电网频率高一个数量级[6],滤波器电容的最大值取决于输入电流的峰值[7]或理想的输出功率[8][9]。这些值在矩阵式变换器低输入电流工作时尤为重要。考虑到式(5)与式(6)

arctan![]() (5)

(5)

![]() =0(6)

=0(6)

则有

C<5.6×10-6iL(7)

或

C<![]() Pout(8)

Pout(8)

C<11.6×10-9Pout(9)

利用基尔霍夫电流定理,得到电容电压的脉动为

![]() (10)

(10)

电容电压波动在低的输入/输出电压传输比和低的功率因数时变大。

由式(9),当功率为3.3kW时,对电容的限制是C<38.3μF这里取5μF/630V。

滤波器的截止频率fc应选择在电网频率(50Hz)和开关频率(20kHz)之间,通常和电网频率和开关频率都有10倍关系,因此,这里我们取fc为1kHz左右。

fc=![]() (11)

(11)

根据上面确定的电容值,可以得到L的取值范围,这里取L为5mH。

4.3 实验验证

在设计好滤波器的参数后,通过实验可以检验参数的选择是否符合要求。

满载时电感上的最大电压降为

![]() (12)

(12)

式中:Un是额定输入相电压;

In是额定输入相电流。

由计算可知,满载时最大的电压降为0.01%。

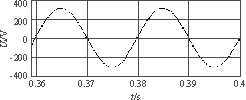

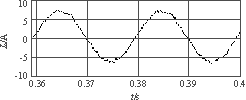

加上滤波器后输入电流的频谱如图7所示,可见输入电流中基波含量占了绝对部分,开关频率及谐波含量已经明显减少,而且由图8可知输入电流和电压基本正弦且同相,因此,滤波器很好地实现了设计要求。

图7 加滤波后输入电流频谱

(a) 输入相电压Ua波形图

(b) 输入相电流Ia波形图

图8 输入电压电流波形对照图

5 结语

电力电子设备的EMI污染越来越受到各方的关注,各国也相继出台了有关EMC的法规。矩阵式变换器(MC)作为一种极具优势的电能利用技术,也必须具有良好的EMC性能。电网的波动会对矩阵式变换器(MC)的工作产生影响,MC也会对电网产生污染,因此,必须采取措施减少开关过程干扰,并增加输入滤波器。本文详细地介绍了MC输入滤波器的设计过程,仿真和实验结果论证了这种设计的可靠性和实用性。