??? 这些损失主要是因为输出驱动器晶体管在导通状态的电阻(Ron)造成,当最大处理电压增加时该损耗增加为降低Ron,设计师要么增加输出器件的尺寸,要么对输出器件进行过驱动,然而随着光刻工艺尺寸的减小,实现会变得更加困难也可以用绝缘栅极双极型晶体管(IGBT)来减少大电流下的等效Ron?

??? 除了优化驱动器输出级的电流/电压性能,IC设计师需要使寄生电流损耗最小寄生电流是因为转移电流从应用侧流过器件而产生的该电流流过内部体二极管,流到高电压电源或从地流出,并导致器件产生额外的功耗设计师需要确保尽量少的电流分别注入或转移到衬底,或从电源输出,以避免驱动器的损坏(闭锁)?

??? 最后一点值得注意的是,由显示IC实现的逻辑功能越来越重要,每个驱动器芯片输出的不断增加需要逻辑部分的更高逻辑密度和速度所有的大屏幕直视显示器驱动器在输入端内置控制电路,大多数这些芯片还在输出级集成转换器因此,需要能实现更有效集成的制造工艺,使得大电压、大电流级与复杂的低电压控制电路在同一个芯片上共存?

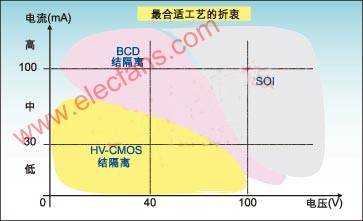

??? 电气因素、寄生效应和控制逻辑三个主要因素的组合影响制造工艺的选择设计师正在努力寻找当前的制造工艺在优势和局限性上的最佳平衡:高压CMOS(HV-CMOS)、双极CMOS-DMOS(BCD)以及绝缘硅(SOI)技术?

??? HV-CMOS是一种标准的MOS工艺,具有用于高压器件的扩展漏极Bipolar-CMOS-DMOS(BCD)是来自意法半导体公司的专有工艺技术,是双极工艺、CMOS工艺和扩散MOS(DMOS)技术的结合在CMOS和BCD工艺中,组件通过反向偏置二极管进行电气隔离,其硅面积与晶体管工作电压成正比这称为结隔离?

??? HV-CMOS在表面传导电流,因此需要额外的硅面积来实现漏极和源极触点,BCD使用垂直MOS晶体管,具有部分内埋入的漏极电极,电流在晶体管内流动对于功率要求高的应用来说,采用BCD工艺的双极器件可以产生最高的电流密度?

??? 尽管存在寄生效应,BCD器件可以设计为工作在寄生器件被触发的条件外,即使在最坏情况下,寄生晶体管的增益也被显著地降低对于指定的器件大小,与采用传统的高电压CMOS工艺的厚氧化物上的PMOS相比,下沉层和埋入层的DMOS结构提供高得多的抗闭锁性能DMOS消除了采用高电压CMOS工艺的高增益寄生晶体管的问题,因此对于给定的电流值提供了更稳定、更小的解决方案?

??? SOI采用了电介质隔离的原理,其中的器件被绝缘的二氧化硅(SiO2)隔离与结隔离相比,在SOI中的绝缘面积实际上与工作电压无关,在采用相同的光刻工艺条件下不影响总的硅片尺寸氧化物隔离层避免了电流漏入到衬底,或者从电源转移,并且寄生电容大大地降低,从而产生较低的功耗和更快的工作频率SOI方法提供非常优越的功率管理、更快的开关频率,以及集成IGBT器件的选项,这对于采用结隔离工艺来说是不可能的然而,这些好处需要平衡考虑因为在SOI结构顶部额外的硅片层带来的附加成本?

??? 对于当今的大尺寸显示器来说,高电压CMOS似乎在更低的电压和电流级别找到用武之地(见图1)

??? 在需要大电流的40到100V之间的电压范围,ST公司专有的BCD技术能实现高集成度、高电压和低成本的最佳折衷然而,随着驱动器输出数量的不断增加(最高达256个输出),寄生效应会相应地成倍数增加,导致功耗增加?

??? 对于电压高于100V的高密度应用,需要在标准BCD工艺中包含SOI特性,以在不牺牲集成密度和抑制IC结构中的寄生单元的条件下承受高的电压通过将硅层与衬底隔离,SOI减少了在开关操作中晶体管需要移动的电荷数量,增加了开关速度,相对于CMOS工艺芯片减少了开关能量?

??? ST的工艺工程师最近开发了0.32um尺寸的带SOI特性的BCD工艺(BCD6-SOI),其目标应用包括90~190V,能保持高于1.4A的电流以及适合实现复杂的系统功能该工艺能有助于降低显示器驱动器的高电压输出级的尺寸,以及能嵌入新的驱动协议,例如RSDS(小摆幅差分信号),并最终通过集成能量恢复控制(ERC)优化功耗