?

雷达信号源的设计在雷达测试中有着非常重要的作用。DDS在相对带宽、频率转换时间、相位连续性、正交输出、高分辨力以及集成化等方面都远远超过了传统频率合成技术所能达到的水平,为系统提供了优于模拟信号源的性能。

FPGA具有集成度高、通用性好、设计灵活、编程方便等诸多优点,因此采用AD9854和FPGA来设计雷达信号源。

1 系统方案概述

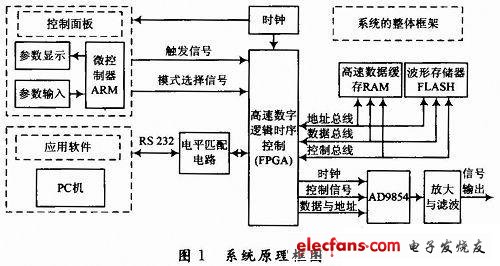

根据雷达信号源系统设计的要求,总体框图如图1所示。

该系统主要由FPGA时序控制部分、AD9854频率合成部分、波形存储三部分组成。在此重点阐述FPGA设计和AD9854硬件设计两部分。

系统的主体部分主要由高速数字逻辑时序控制模块(FPGA)和DDS芯片AD9854构成,还包括放大模块、滤波模块、存储模块、时钟模块、电源模块。该部分通过FPGA对整个电路的数字部分进行时序控制,包括给AD9854发送数据、地址、时钟以及控制信号。AD9854是DDS芯片,能产生所需要的信号。存储部分采用了FLASH和SRAM;FLASH主要用来存储波形文件,而SRAM主要是在开机时暂存数据文件。

通过控制面板发送触发信号和模式选择信号对系统信号产生进行控制。当FPGA接收到触发信号时,FPGA才开始工作,并且给AD9854发送数据以产生信号。模式选择信号是3位的二进制数,可以产生8种状态。控制面板和FPGA通过RS 422电平相连,通过差分数据线来传输数据。

PC机应用软件完成所需各种软件的波形数据的计算,包括起始频率FTW,频率分辨率DFW,时间分辨率RRC等数据,然后将所得的数据转化成.dat格式。PC通过串口与系统主板进行数据通信,通过MAX3232进行电平转化。数据最后存储到主板的存储器中(FLASH和SRAM);当系统工作时,FPGA从FLASH中读取波形文件来产生信号。

2 AD9854模块

2.1 AD9854芯片介绍

数字频率合成芯片AD9854是用于高端DDS技术的一款芯片,该芯片带有两个高速、高性能的正交D/A转换器,可以同时输出I/Q两路正交信号。当参考时钟源很精确时,AD9854能够产生高稳定度的,频率、相位、幅度均可编程的正弦和余弦曲线,被广泛地应用于通信、雷达、仪器等应用领域。AD9854的高速DDS内核能够提供48 B的相位累加器和频率累加器(在300 MHz的系统时钟下,可达1μHz的频率分辨率);其中17 B的相位-幅度映射位数能够确保该芯片优良的无杂散动态范围(SFDR)性能。

2.2 AD9854芯片工作模式

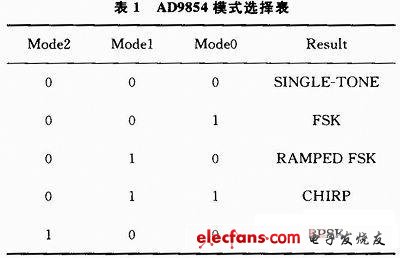

AD9854具有5种可编程操作模式,通过改变控制寄存器(并行寻址方式下的地址为1FH)的控制位即可以选择相应的模式。根据本方案,主要对单频(Single Tone)模式和调频(Chirp)模式进行探讨。5种模式的选择表如表1所示。