引言

当今许多工业和仪器仪表应用都涉及到传感器测量技术。传感器的功能是监测系统的变化,然后将数据反馈给主控制单元。对于简单的电压或电流测量,传感器可以呈阻性。但在某些传感器系统中它却呈感性或容性,这意味着传感器在其工作范围内的阻抗变化呈非线性。

这种复数传感器的典型例子是接近传感器——用来确定相对移动物体的距离;以及容性传感器或感性传感器——在医学行业中用来测量血液流速以及分析血压或血质。

测量这些“复数传感器”的阻抗需要一个在传感器频率范围内扫描的激励源。本设计思想表明如何能够方便地使用单芯片数字波形发生器提供这种大于10 MHz的频率扫描。本文也将介绍一种集成激励源、模数转换器(ADC)和信号处理的完整单芯片阻抗转换器(IDC),从而使它适合需要高达约达50 kHz激励频率的应用。

传感器:工作原理

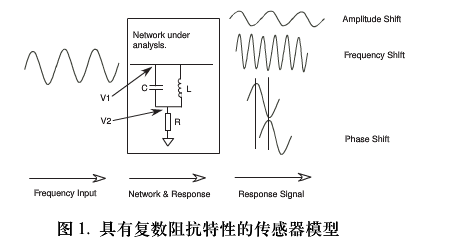

图1示出一种具有感性阻抗或容性阻抗特性的传感器模型。

通过传感器的激励频率根据其电感(L)或电容(C)的瞬态值变化将表现出一种幅度、频率或相移变化。例如,超声波液体流量计通常表现为相移变化,而接近传感器则是幅度变化。

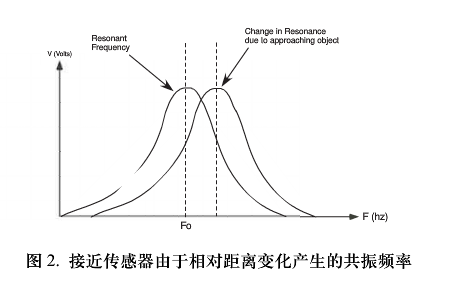

跟踪这种阻抗变化的最常用的方法就是监测电路的共振频率。共振频率是指电容值等于电感值时对应的频点,这也是频率曲线上的最大阻抗处对应的频点。例如,考虑图2所示的接近传感器的情况。在正常工作模式下,即静态条件下,传感器的L、R和C具有唯一的值,这种情况在共振频点将具有最大阻抗。当移动物体接近传感器时,传感器的L和C值会发生变化,从而产生了新的共振频率。如果监测共振频率的变化(从而监测阻抗)可以预测移动物体相对传感器的距离。

计算共振频率

计算电路的共振频率需要一个交流(AC)激励信号源,它在一段频率范围内扫描以绘出如图2所示的频率与阻抗关系曲线。AD9833单芯片数字波形发生器可提供一种产生这种扫描输出的简单、低成本方法。我们通过写入代表所需频率的数字码字来改变输出频率。AD9833具有两个频率寄存器,从而允许用户在对一个频率寄存器编程的同时输出第二个频率寄存器。

AD9833具有许多优点:输出频率的分辨率是28 bit,所以用户能够以小于0.1 Hz的步幅增加输出频率。其输出频率范围是0~12.5 MHz,从而提供很宽的传感器选择灵活性。例如,有些传感器具有很低的频率范围,但在该频率范围内需要很高的分辨率;而另外一些传感器则需要以较低的分辨率调节很宽的频率范围。

使用频率扫描方法,可以很容易地计算出传感器的共振频率,并且可以利用该数据提供许多应用的传感器检测信息。

系统框图

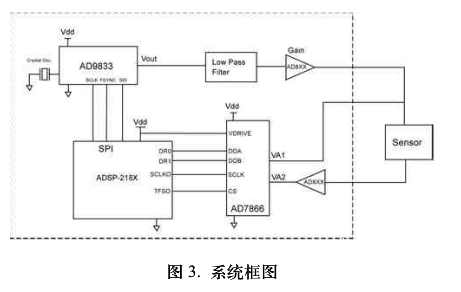

图3示出实现这种测量的系统框图。AD9833数字波形发生器可通过ADSP-218x数字信号处理器(DSP)对其设置。首先必须对AD9833的正弦输出电压波形进行低通滤波以去除来自主时钟(MCLK)、镜像频率和高阶频率的馈通。然后将经过滤波的信号用作传感器的激励信号。根据传感器的阻抗变化,将响应信号放大以使其适合ADC的动态范围。传感器的输出和激励频率都馈送到AD7866 12 bit 1 Msps同步采样双ADC。在将ADC的输出数据馈送到DSP,以便通过计算传感器的幅度和相位变化做进一步的分析。

完整的集成传感器解决方案

图3所示的分立解决方案虽然有助于各种通用传感器的阻抗测量,但使用的宽带元件使该其成本昂贵。单个分立元件会增加其自身的误差源,并且有源元件会增加相位误差,所以必须经过校正将这些误差消除掉。一定需要DSP处理复杂的数学运算,并且还可能需要外部存储器来存储ADC的原始数据,这样会进一步增加成本。

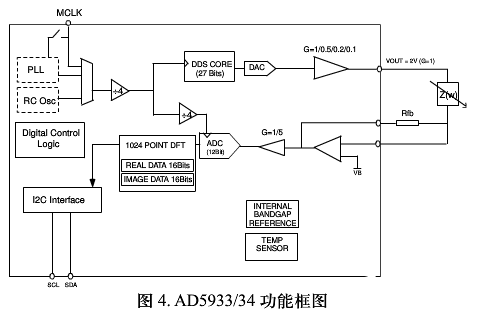

如果仅需低频传感器分析,我们可提供一种低成本的解决方案。AD5933/34 12 bit IDC和网络分析器将上述主要处理框图集成到一颗单芯片集成电路(IC)。图4示出其功能框图。

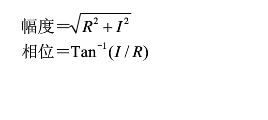

频率发生器允许使用高达50 kHz的已知频率激励100 Ω~20 MΩ范围的复数阻抗。响应信号由内置ADC采样。内置DSP引擎完成ADC输出的离散傅立叶变换(DFT)。然后DFT算法返回实部(R)和虚部(I)数据字,从而允许方便地计算其阻抗。使用以下公式可以方便地计算阻抗的幅度和相位。

我们使用频率扫描来确定实际的实部阻抗值Z(ω)。我们可以在每一个频点计算阻抗,并且可以建立频率与幅度的关系曲线。

用户可以设置2 V、1 V、500 mV或200 mV的峰峰值正弦信号作为外部负载的激励源,并且可达到27 bit(小于0.1 Hz)的频率分辨率。

为了完成频率扫描,用户首先必须设置扫描所需的工作条件:起始频率、频率步幅以及步数,然后需要一个启动命令开始扫描。在每一点扫描频率处ADC都完成1024点采样并且计算DFT以为波形提供实部和虚部数据。将该实部和虚部数据通过I2C接口以两个16 bit字的形式提供给用户。如果其内置DSP有处理引擎,则意味着用户不必处理复杂的数学计算。它也无需存储ADC原始数据,仅需返回两个16 bit的字。还可以采用降低功能和降低成本的DSP解决方案,因为已经显著地降低了对处理能力的要求。阶跃响应的增益可设置为1或5倍。其ADC是一款3 V电源供电的低噪声、250 ksps或1 Msps采样率的高速ADC。系统时钟通过MCLK端的参考时钟从外部提供,MCLK可从外部晶体振荡器或通过内部PLL单元提供。