用PAC-Designer 设计滤波器

近年来,数字系统的EDA技术及可编程逻辑器件的发展极大地改变了传统电子系统的设计思想和实现方法,但是模拟电路的设计手段似乎还停滞不前。现在,由美国LatTIce公司推出的模拟电路在系统可编程技术ispPAC使这种情况发生了变化,为模拟电路的设计自动化翻开了新的一页。

ispPAC 及PAC-Designer的特点

与数字系统的在系统可编程技术类似,模拟电路的在系统可编程技术允许设计者使用开发软件在计算机中设计和修改模拟电路,并通过编程电缆将设计方案下载到可编程模拟器件中,从而加快设计进程,提高系统设计的准确性,为电子系统设计人员开发产品提供了一条崭新的途径。目前由LatTIce公司推出的在系统可编程模拟器件有ispPAC10、ispPAC20和ispPAC80三种,这些芯片都是基于E2CMOS编程,支持JTAG编程方式,可编程十万余次。ispPAC器件的开发软件为PAC-Designer,采用原理图输入方式,并能对设计电路作幅频特性和相频特性仿真。

PAC-Designer软件在滤波器的设计方面独具特色,其内部集成了不同的宏功能,在宏功能中可以选择滤波器的类型(如巴特沃斯或赛贝谢夫)和参数(增益、截止频率、品质因数等)来实现所需的滤波器。

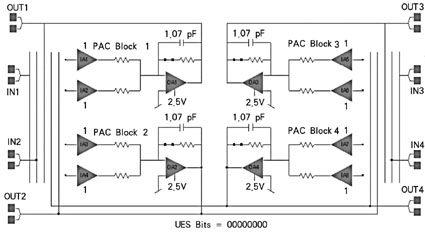

ispPAC10的内部结构

ispPAC10是LatTIce公司推出的在系统可编程模拟器件,采用非易失性数字E2CMOS技术,其内部由四个完整的模拟宏单元PACBlock组成,每个PACBlock又由运放、电阻和电容组成,如图1所示。芯片无需外围元件就可以灵活实现精密滤波器、求和、求差、增益、衰减和积分等基本模拟功能。用ispPAC10设计电路时,PACBlock中的运放增益可在-10~+10之间进行调节,电容可以在一组固定值之中进行选择,运放与一系列的反馈电容组合可以产生120种可编程电路,频率范围在10kHz至100kHz之间,从而完成不同的电路功能。

用PAC-Designer和ispPAC10设计滤波器

用手工设计二阶滤波器时,需要通过理论公式不断修订各元件参数,最后才能满足电路指标的要求,而Pspice和 EWB等软件一般只能进行模拟仿真,而且仿真实现的电路还必须通过分离元件来完成实际电路。

EWB等软件一般只能进行模拟仿真,而且仿真实现的电路还必须通过分离元件来完成实际电路。

采用ispPAC10设计带通或低通滤波器时,不需要任何外部元器件就可以对整个电路的增益、Q值和截止频率进行调整。通过设定运放增益和电容参数,可以将PACBlock配置成可编程的单极性低通滤波器或积分器,在ispPAC10内部的几个PACBlock还能够连接在一起组成更高级数的滤波器。

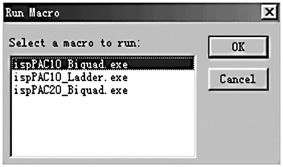

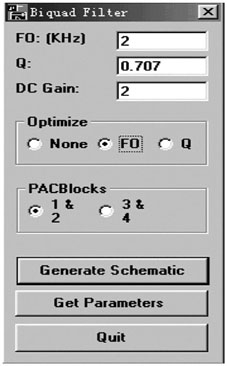

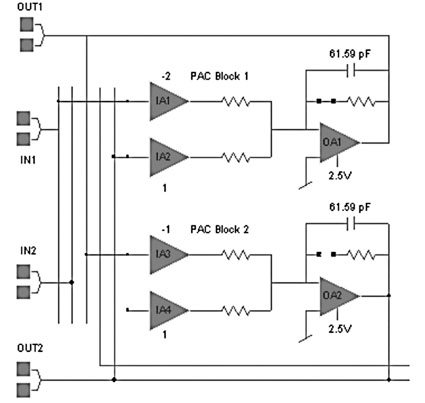

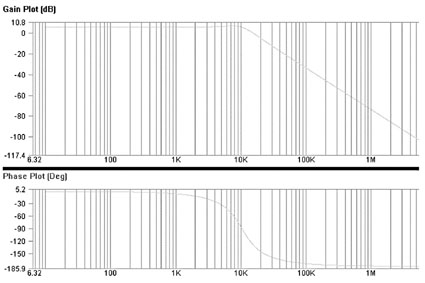

用PAC-Designer宏功能,只要输入滤波器的参数,系统就会根据设计要求算出反馈电容、电阻及各运放的增益等参数,然后在电路图编程环境中进行电路布线,修改其参数值。具体过程是,首先打开Tool菜单,选择Run Macro,弹出如图2所示的宏功能对话框,选择“ispPAC10 Bipuad.exe”,在参数输入对话框中填入F0=2kHz,Q=0.707,DC Gain=2,在OpTImize中选择F0,就可得到截止频率为2kHz,Q为0.707,增益为2的二阶低通滤波器,图4是滤波器的原理及内部接线图。保存原理图,再对其进行幅频及相频特性仿真,仿真结果如图5所示。观察波形,确认各项参数指标无误后,最后将设计下载至ispPAC10芯片中。设计方案的下载是通过编程电缆将计算机的并行口和被编程器件连在一起来实现的,接口符合IEEE1149.1JTAG标准。如果目标电路板上有多个可编程器件,需采用菊花链的连结方式将几个器件连在一起。

结束语

在系统可编程模拟器件及设计工具的出现,使模拟电子系统的设计与实现方法发生了很大变化。运用PAC-Designer及ispPAC系列芯片设计滤波器及其他模拟电子线路,将大大缩短产品的开发周期,提高系统的可靠性并减少制造成本,应用前景非常广阔。