Mentor Graphics的Tanner EDA软件是一套针对定制集成电路(IC)、模拟/混合信号(AMS)和MEMS设计的产品。对物联网(IoT)需求的突然上升使全流程混合信号设计环境面临独特的要求:经济实惠且易于使用,但功能强大,可创建部署物联网所需的各类产品。

简介

Mentor Graphics的Tanner EDA软件是一套针对定制集成电路(IC)、模拟/混合信号(AMS)和MEMS设计的产品。对物联网(IoT)需求的突然上升使全流程混合信号设计环境面临独特的要求:经济实惠且易于使用,但功能强大,可创建部署物联网所需的各类产品。虽然许多EDA工具供应商为AMS设计提供软件,但这些工具不是成本太高(性价比低),就是定制点解决方案需要大量数据操作和手动集成。Tanner EDA软件AMS IC设计流程具有其独特的优势。它提供了紧密集成的混合信号设计套件,设计周期极短、性价比高,特别适合物联网和基于项目的设计。

前端设计

电源管理、显示器、图像传感器、光伏、生命科学、汽车、航空航天和消费类电子产品等器件所服务的应用和细分市场种类繁多,与AMS集成电路相关的设计挑战也多种多样。但是,在AMS设计方面,物联网将会产生最大的影响。

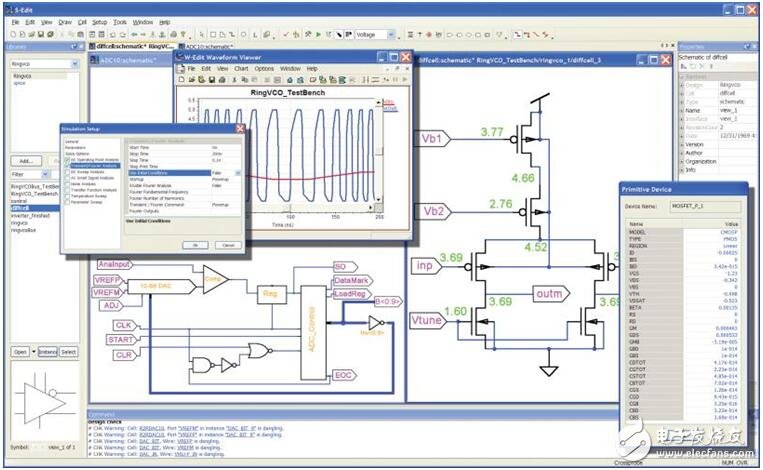

图1:Tanner S-Edit SchemaTIc输入设计和仿真平台,显示了原理图、仿真波形、模型参数和仿真设置

在创建模拟/混合信号设计时,设计人员需要对两个领域进行权衡。设计人员越快找到最优解决方案,就能获得更多时间来解决棘手的极端情况。具体而言,Tanner T-Spice AMS支持Verilog-AMS建模,通过基于高级方程式针对混合了行为的Verilog数字模块的仿真模块进行建模,从而实现复杂混合信号IC的自顶向下的设计。设计人员可以快速探索混合信号架构,然后在详细设计单个模块时使用抽象的Verilog-AMS模型作为执行规范。

Tanner S-Edit原理图输入是一款前端设计工具,为创建模拟/混合信号设计所需的多视图单元提供简单易用的设计环境。S-Edit支持已绘制的原理图视图、以及SPICE、Verilog、Verilog-A和Verilog-AMS视图,因而设计人员能够轻松地以单元为基础交换抽象或详细模型。S-Edit通过Open Access或通过Cadence、Pyxis、Laker、OrCAD和ViewDraw的EDIF导入原理图并自动转换原理图和属性,以实现兼容数据的无缝整合。设计人员可以使用S-Edit的原理图设计检查功能快速找出常见错误,例如未驱动的网络、未连接的管脚以及由多个输出驱动的网络。在运行仿真之前发现错误能够提高设计效率和速度,对AMS设计而言尤其重要。

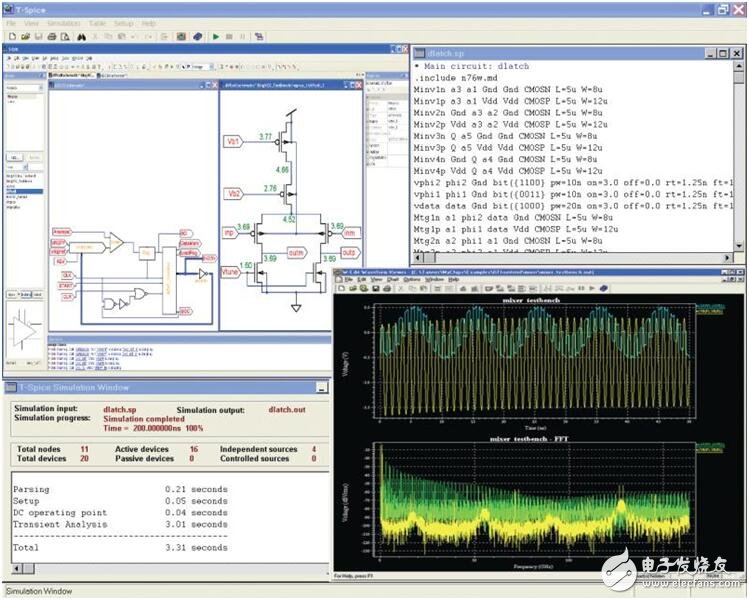

接下来是高精度的设计仿真。考虑到电路规模越来越大,复杂性越来越高,且需要支持各种晶体管和行为模型,这个任务对混合信号设计而言并非易事。Tanner T-Spice SimulaTIon支持广泛的标准,具备经市场验证的可靠性、高性能和可扩展性,能够应对这些挑战。T-Spice提供与HSPICE和PSpice兼容的语法,支持行业最新模型,包括PSP、BSIM3.3、BSIM4.6、BSIM SOI 4.0、EKV 2.6、MOS 9、PSP、RPI a-Si & Poly-Si TFT、VBIC和MEXTRAM多种模型,从而通过全范围的晶圆代工厂模型轻松进行现代设计和传统设计的仿真。T-Spice使设计人员能够使用虚拟数据测量、蒙特卡罗分析和参数扫描准确地描述电路行为的特征。它还支持Verilog-A进行模拟行为建模,使设计人员能够在进行器件的整体设计之前,验证系统级的设计。

图2:Tanner T-Spice Simulator图形用户界面包括:原理图、SPICE网表、仿真日志和波形数据

此外,T-Spice还可以利用Mentor Graphics ModelSim数字仿真器进行高性能的混合信号仿真。设计人员可以结合使用Verilog、Verilog-A、Verilog-AMS和晶体管层级的SPICE加载网表。T-Spice可自动分割网表并启动AMS协同仿真,同时在处理任何SPICE或Verilog-A设计时,将任意数字模块发送到ModelSim。只要信号在模拟/数字边界发生变化,T-Spice和ModelSim就会协同仿真并互相通信。

完整的物理版图功能

前端设计和验证工作完成后,接下来就是物理版图了。设计人员必须再次权衡优先顺序,尤其是设计的模拟部分。再次重申,Tanner能够提供基于PC平台的最优功能组合,易学易用。Tanner L-Edit IC Layout工具是一款完整的层次化物理版图编辑器,结合了快速渲染工具和内置效率工具,使设计人员在创建用于设计的版图时能够最大限度地提升效率。该工具的编辑功能经过优化,所需的鼠标操作比任何其他版图编辑器都要少。内置效率功能包括对象捕捉、对齐工具、自动生成保护环、针对任意形状和曲率的多边形对象的复杂布尔运算,以及原理图与版图之间的交互显示。

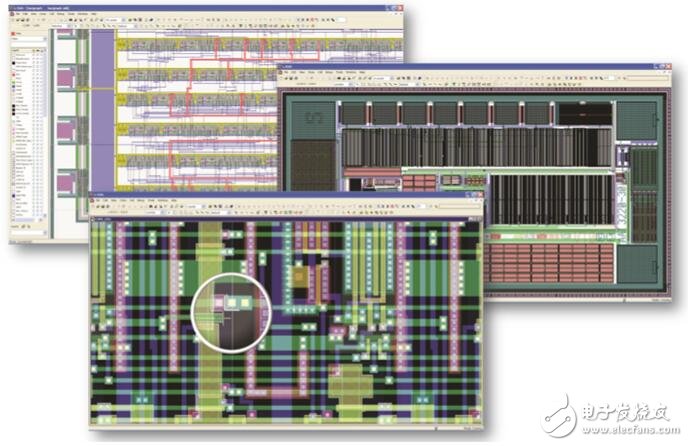

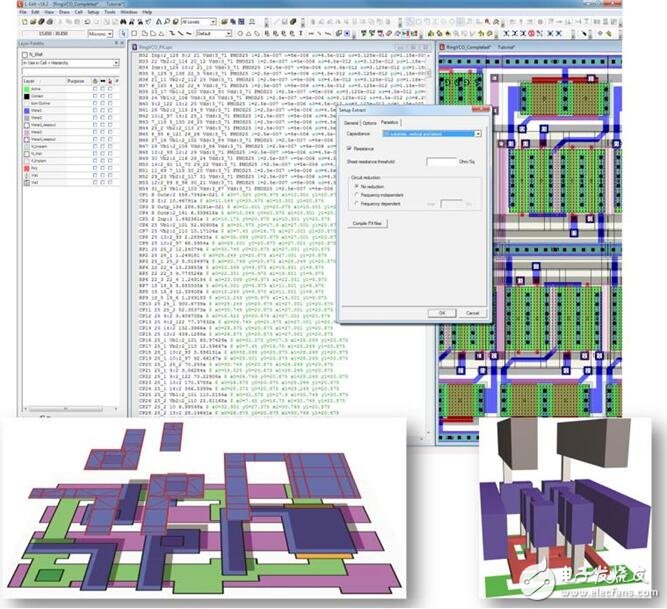

图3:Tanner L-Edit IC Layout 工具显示三种设计的版图数据

L-Edit支持参数化单元设计,使设计人员能够自动化地创建自定义版图生成器或使用DevGen轻松设置针对MOSFET、电阻器或电容器等常见器件的版图生成器。该工具的交互式设计规则检查(DRC)功能可以在版图编辑时实时显示违规情况,帮助设计人员能够一次性成功创建简洁、无误的版图。此外,通过L-Edit的节点高亮显示功能,设计人员可以高亮标出所有连接至节点的几何图形,从而快速发现并修复短路和开路等LVS问题。

L-Edit通过支持多个用户在同一版图工作来提升设计效率。设计人员可以直接使用晶圆代工厂提供的文件,无需手动设置。从而减少了物理设计工具中 CAD支持负担,使设计人员能够集中精力进行设计。

版图布局团队可以通过完整的原理图驱动版图流程来最大化效率。S-Edit和L-Edit保持通信与同步,包括交互显示和ECO标记。基本元件、子单元和参数化单元的自动实例化可节省时间并预防错误,而实时飞线和辅助性手动布线可以最佳方式快速进行设计布局和布线。

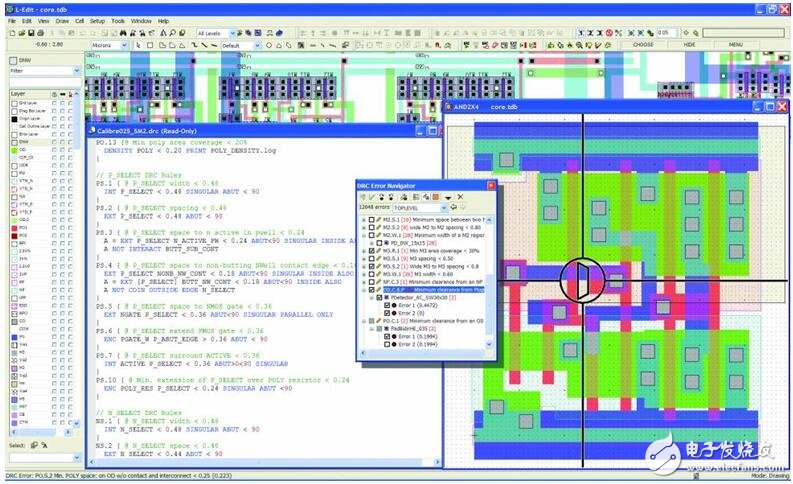

物理验证

Tanner Verify DRC和LVS工具提供了全面且经济的物理验证解决方案。这些工具可执行模拟/混合信号IC设计规则检查(DRC)和网表提取。单元中出现违规情况时,层次化规则检查引擎能够在第一时间发现,使设计人员得以马上更正违规之处,而不是在多次重复违规之后才发现问题。另外,该工具可与Tanner L-Edit IC Layout集成,从而能精确找出错误、快速修改并加快调试速度。

图4:Tanner L-Edit IC Layout在语法高亮显示编辑器中显示设计规则检查、DRC运行结果、以及针对特定规则违规情况的错误标记

建模版图的作用

对先进的工艺节点(以及频率更高、电压更低的相关电路)而言,互连寄生参数已然成为一个巨大的挑战。随着工艺尺寸变小,互连厚度增加,以此抵消因互连宽度减小而导致的电阻增加。这就使得横向耦合电容的影响比垂直耦合电容要大得多。横向耦合可以导致不同的时序行为,要准确计算出延迟和电路行为,就必须将其包含到仿真中。

Tanner ParasiTIc ExtracTIon是一款高性能的寄生参数提取工具,作为可选的插件提供。该工具可与Tanner L-Edit IC Layout集成,从而能够轻松快速地提取寄生参数。它可以从版图中快速提取处于仿真就绪状态的SPICE网表,包括器件(MOSFET、双极晶体管等)和互连寄生参数。Tanner Parasitic Extraction还可以提取针对各个节点的精确的、完整的寄生网络,包括垂直和横向耦合电容以及互连电阻。此外,通过内置的网表约简算法,该工具可以在无需将仿真精度降低至用户指定频率的情况下简化RC寄生网络。

图5:通过反向标注互连寄生模型仿真环型振荡器

精简的数字物理设计

在创建绝大部分电路是模拟电路、少部分电路是数字电路的设计时,即所谓的“大A小D”(Big A/little D)设计,模拟设计人员面临着诸多挑战。从概念层面来看,模拟设计团队最初面临的困难是针对混合信号电路进行自顶向下的整体设计。在整个设计流程中,他们要面对来自多个领域的挑战。例如,设计人员可能很难掌握数字逻辑为内部状态或隐藏状态的数字电路的边缘情况或问题。全芯片时序分析对设计人员来说通常很难应付。如果存在颇具规模的数字部分,他们就很难完成整个时序分析。最后,在物理验证方面,数字逻辑产生的噪音对具备相同基底的模拟电路来说就可能会太大。

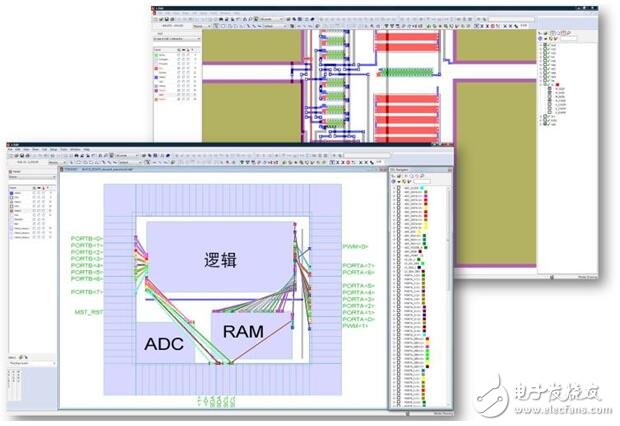

Tanner套件专用于解决这些挑战。使用混合信号工具的模拟设计人员可受益于其更强的自动化、更高的准确性、更低的NRE成本以及更短的上市时间。为此,Tanner解决方案采用了专门针对“大A小D”AMS市场的从RTL到GDS的完整流程。这是一款完整的逻辑合成工具,具备针对区域、电源、时序和可测试性设计(DFT)的合成与优化功能。Tanner Place and Route与L-Edit高度集成,使设计人员可以完全掌控布局和布线流程中的每个步骤。TimeCraft是一款速度快、容量大的静态时序分析器(STA),可用于纳米时序分析和Sign-off。(请注意,ModelSim可提供使用布局后布线信息的动态时序分析。)

全芯片组装

任何全面的模拟/混合信号流程将包含全芯片组装过程,即将主要功能模块置入压焊框并进行顶层信号和总线的布线。

图6:Tanner L-Edit IC Layout的原理图驱动版图展示了实时飞线并支持手动、人工辅助和全自动的布线模式

Tanner的全芯片组装解决方案通过S-Edit和L-Edit的SDL接口实现。以顶层模块为例,设计人员可以使用SDL的实时飞线摆放模块,以尽量减少布线拥塞。设计人员还可以使用SDL的短路和开路检查器快速检查连接问题,该检查器无需运行完整的LVS便可在单元环境中运行并高亮显示错误。

SDL Router是一款与SDL集成的自动布线引擎,可以加快模拟单元的版图和顶层芯片组装的布线。该工具使设计人员得以集中精力在要求精细的布线上,以便操作或处理对模拟敏感的部分或全部网络。对所有剩余的电路,SDL Router可自动为非关键网络布线,以不同的用户指定宽度为不同网络布线,支持用于图层转换的多个通孔。设计人员还可以通过它将现有的几何图形标记为特定网络的一部分,然后通过网络按照设计人员的意图选择、高亮显示和拼接几何图形。

结语

2015年3月,Mentor Graphics收购了Tanner的业务资产,利用其雄厚的技术领导力和全球分布网为致力于从事IC、MEMS到IoT器件的各种混合信号项目的设计人员提供支持。这些设计人员面临着各种各样的挑战,大多数与IC的功能和复杂性持续增加有关。同时,业务压力迫使设计人员必须要缩短上市时间和减少返工。Tanner套件从基础开始建造,以设计人员的需求为核心。一些EDA工具供应商提供了用于AMS设计的软件,但这些工具不是成本太高(性价比低)、就是需要大量数据操作和手动集成的自定义点流程工具。Tanner套件能够为AMS设计人员提供一致而全面的工具套件,实现业内无可匹敌的效率、可用性和性价比。