数字电路作为一门专业基础课,除了介绍数字电路的理论知识外,更需要通过配套的实验平台将理论知识和实践环节相结合,培养学生的动手能力和实践创新能力。为此,自主开发了基于 FPGA 的数字电路“口袋实验室”。该“口袋实验室”基于目前流行的FPGA 芯片开发,已经实际应用于数字电路教学实践中。

1总体设计

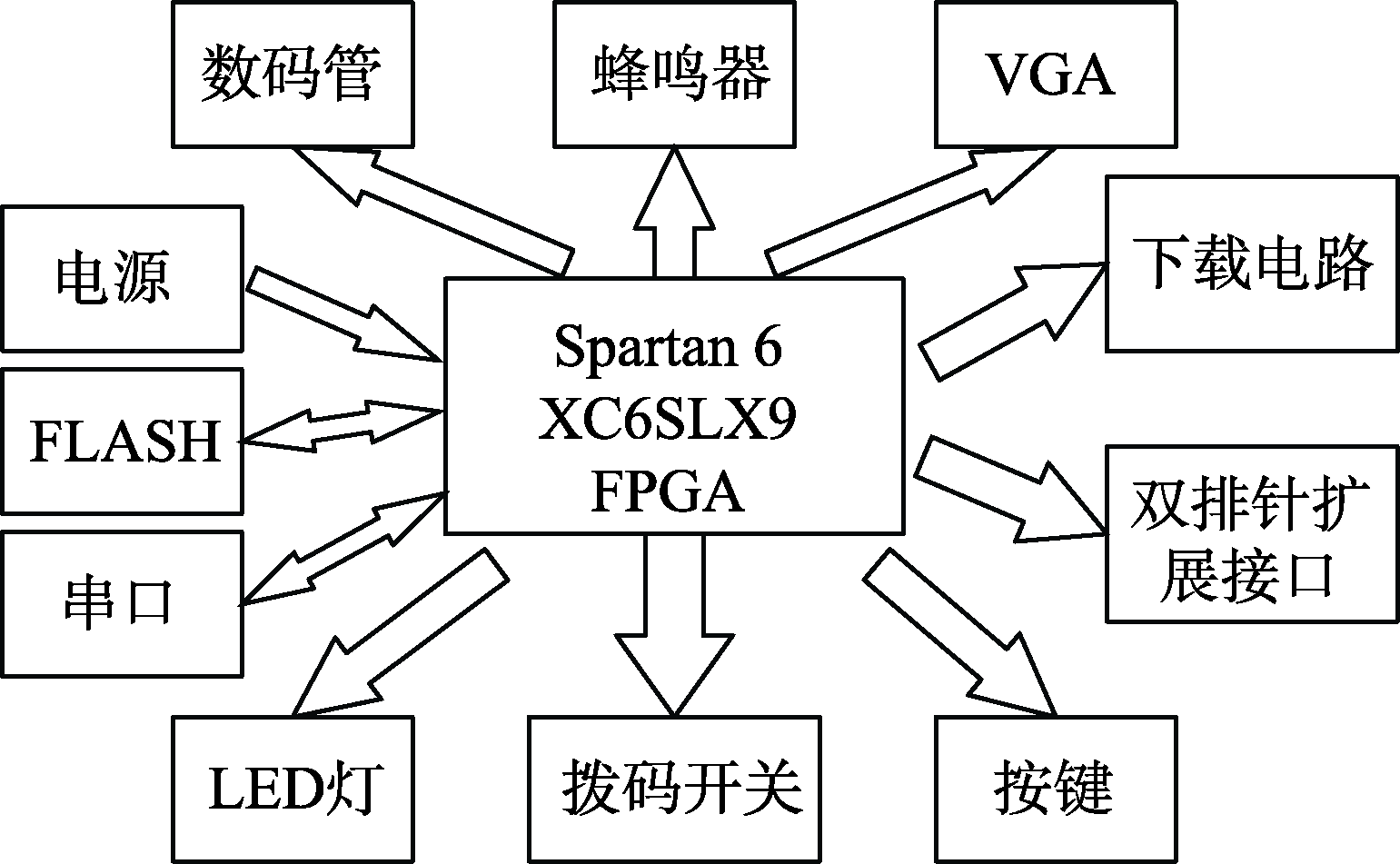

“口袋实验室”的电路包括电源、FPGA、下载电路、数码管、VGA 接口、拨码开关、按键、LED 灯和双排针扩展接口。其总体框图见图 1,实物图见图 2。

图 1 系统总体框图

图 2 系统实物图

设计中预留了 30 个扩展接口,由双排针引出,其中 24 个是 FPGA 的通用 I/O,3 个 3.3 V 引脚和 3 个地引脚。串行通信采用 CH340G 串口芯片,用于 FPGA 和 PC 机之间的通信。“口袋实验室”拥有 2 个 4 位共阳极数码管、1 个无源蜂鸣器、1 个八位拨码开关、1 个 VGA 接口以及 10 颗 LED 灯和 6 个按键,可以满足数字电路基本的实验需要。

2电路设计

2.1电源电路

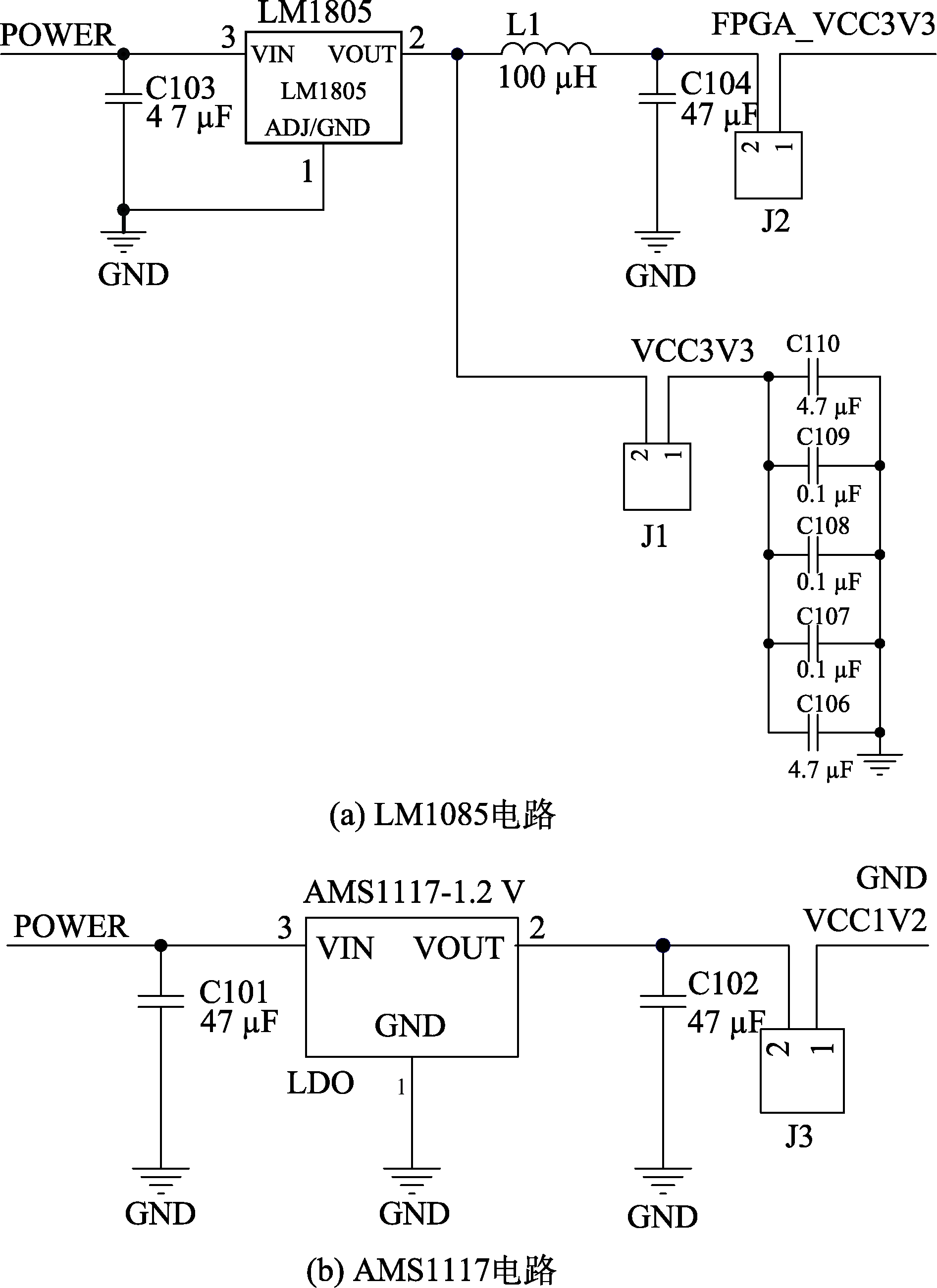

电源系统为整个系统提供能量,是系统的基础。采用 LM1085 芯片提供 3.3 V 电压,采用 AMS1117 芯片提供 1.2 V 电压。

考虑到XC6SLX9 的 3.3 V 电源和其他外设共用一个电源芯片,为保证其他外设电流突变时不影响XC6SLX9 的正常供电, 使用一个功率电感以隔离FPGA 和外设的电源。具体电路设计见图 3。

图 3 LM1085 电路和 AMS1117 电路

XC6SLX9 对电源的要求较高,电源引脚附近需要多个去耦电容,以减小电源瞬变,保证电源完整性。电源部分还设计有 1 颗LED 灯用于指示FPGA 电源是否正常。

2.2配置电路设计

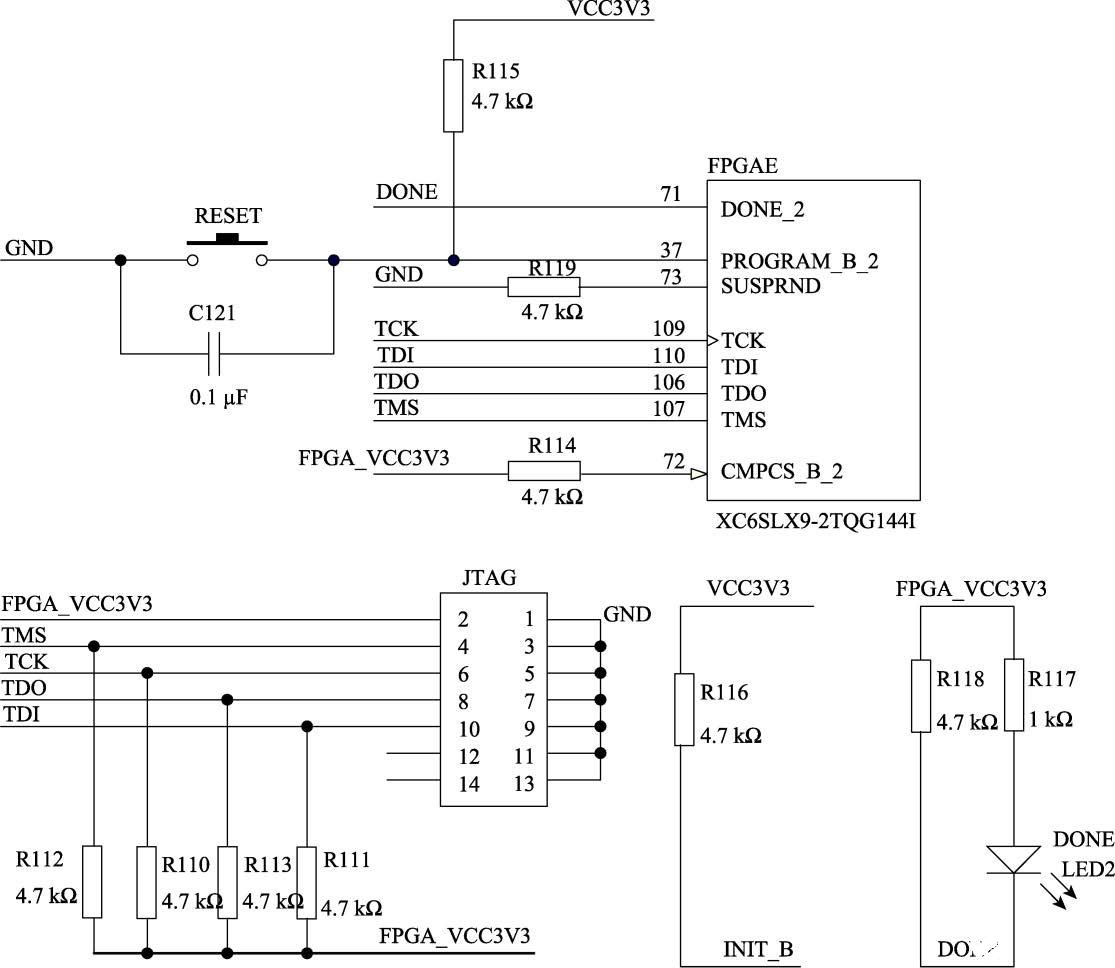

配置电路一个是使用 JTAG 配置的电路,另一个是使用 FLASH 的主动 SPI 配置电路。

2.2.1JTAG 配置电路

JTAG 配置电路见图 4。

图 4 JTAG 配置电路

JTAG 的主要引脚 TMS、TCK、TDI、TDO 经 4.7 kΩ

电阻上拉,以保护电路。JTAG 引脚在印刷电路板(PCB)上通过 14 针 2.0 mm 间距的简易牛角座引出。简易牛角座采用防反插设计,以保证 JTAG 连接正确。

PROGRAM_B 引脚默认上拉,通过按键接地,可以用于 FPGA 的软复位。DONE 引脚上拉,且有 LED 指示 FPGA 是否配置完成。

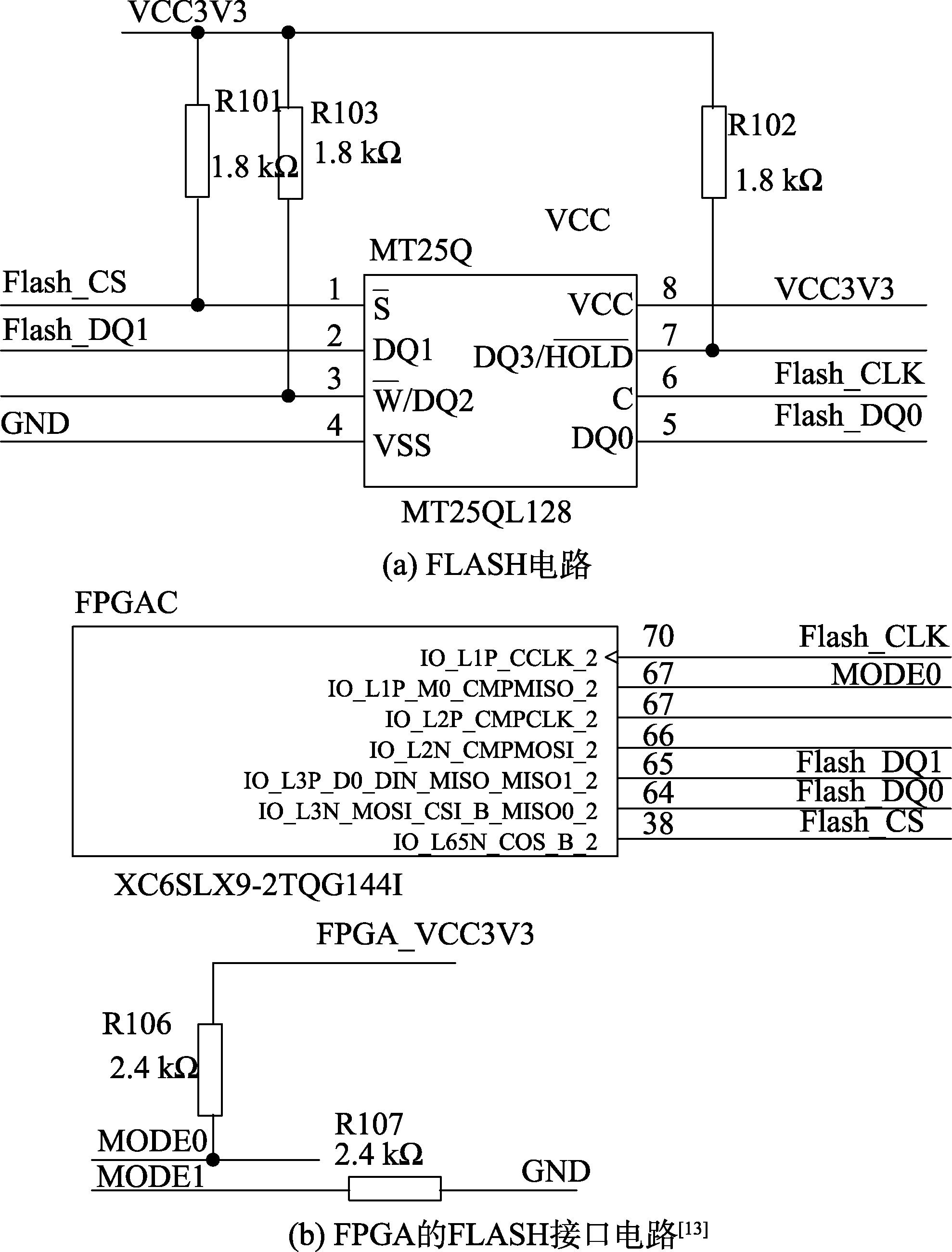

2.2.2FLASH 电路

设计所选用的 FPGA 基于 SRAM 工艺,掉电后不能保存数据,因此在重新上电之后必须从外部的配置存储器加载配置。FLASH 电路见图 5(a)。MODE0 和MODE1 的电平决定了 FPGA 的配置方式,当 MODE0 拉高以及 MODE1 拉低时,FPGA 使用主动 SPI 配置模式。接口电路见图 5(b)。

图 5 FLASH 电路和 FPGA 的 FLASH 接口电路

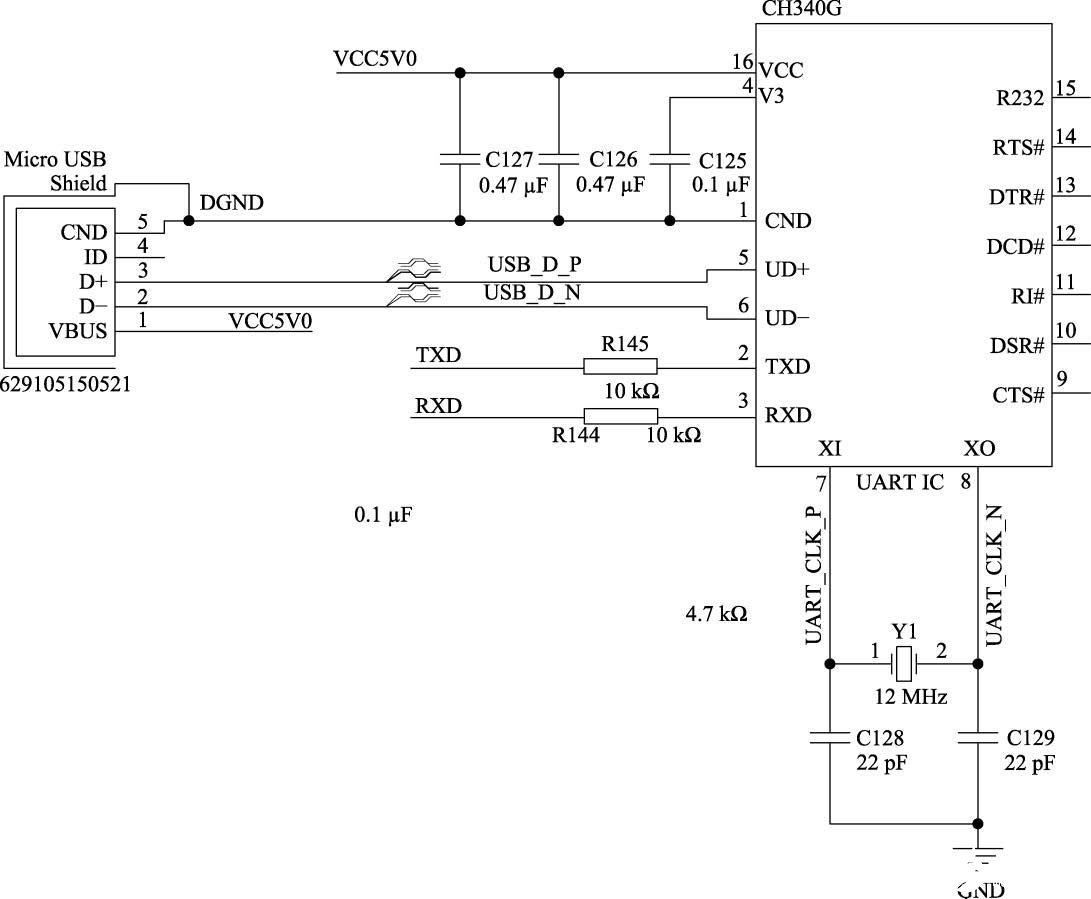

2.3串口通信设计

选用 CH340G 作为 FPGA 和 PC 机之间通信的转换芯片。CH340G 是常用的USB 转串口的芯片,兼容 5 V 系统和 3.3 V 系统,由于本设计中选用的 XC6SLX9 属于 3.3 V 系统,因此 CH340G 的供电电压设置为3.3 V,如果供电电压调整为 5 V,则串口通信将发生故障,数据不能通过串口发送至 PC 机。串口部分电路见图 6。

图 6 串口通信部分电路

2.4 扩展接口设计

为保证“口袋实验室”的扩展能力,在设计时将FPGA 的 24 个通用 I/O 口通过双排排针在 PCB 上引出,可供使用者外接电路。

为了防止 FPGA 的 I/O 接口接入过高的电压或者通过过大的电流而损坏 FPGA,设计中使用双向电平转换芯片 TXS0108E 对 FPGA 的 I/O 口和外部接口进行隔离,以保护 FPGA 芯片。

3实践教学实例

3.1数码管显示实验

实验要求使用数码管显示时间精度为 100 ms 的秒表,最低位数字每 100 ms 加 1。

3.1.1实验硬件电路

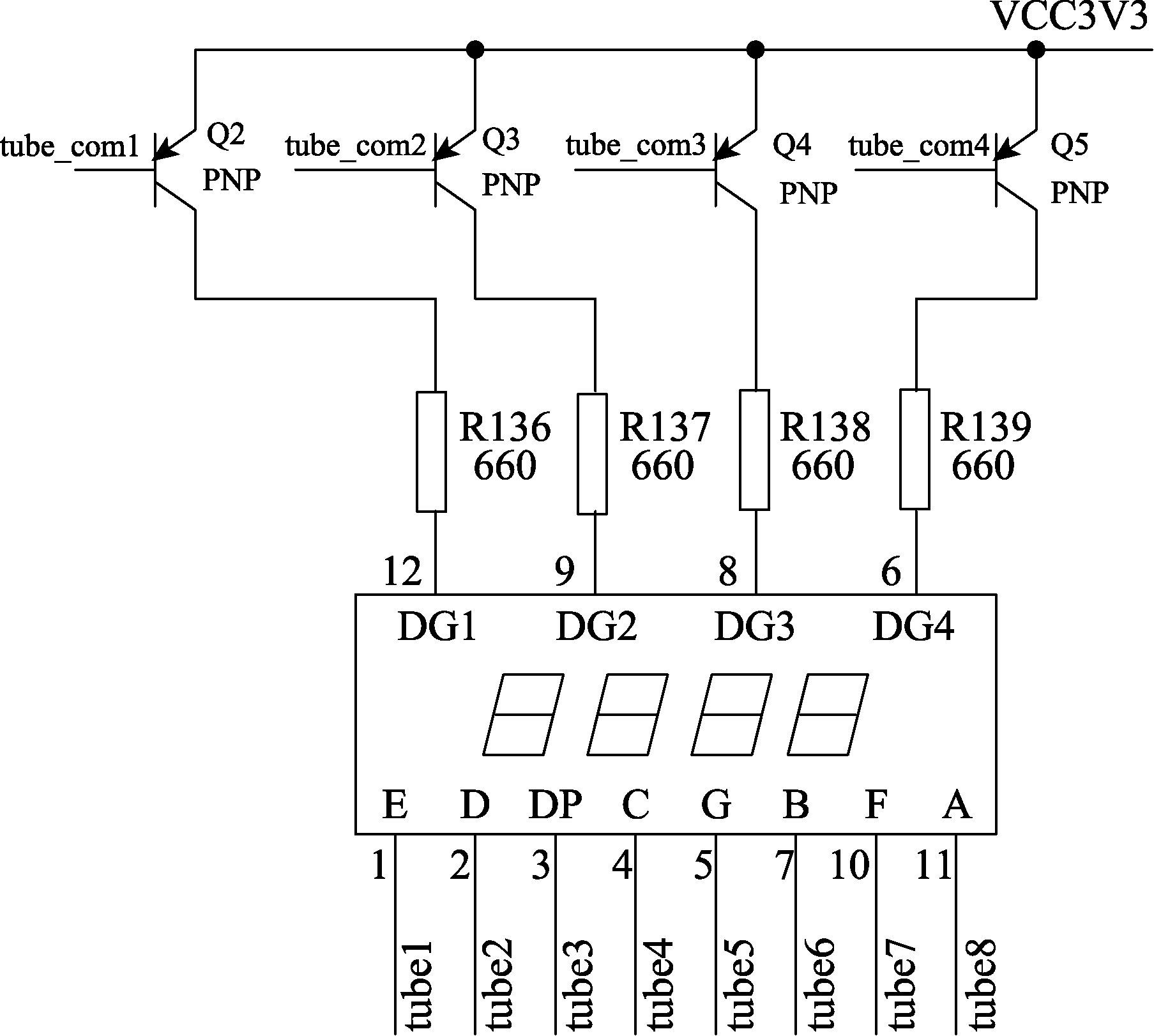

“口袋实验室”选用的数码管是 4 位共阳极数码管,其中公共端使用三极管驱动,其余 A、B、C、D、E、F、G、DP 8 个引脚分别和 FPGA 的 I/O 口连接。电路如图 7 所示。

图 7 数码管电路

3.1.2FPGA 代码设计

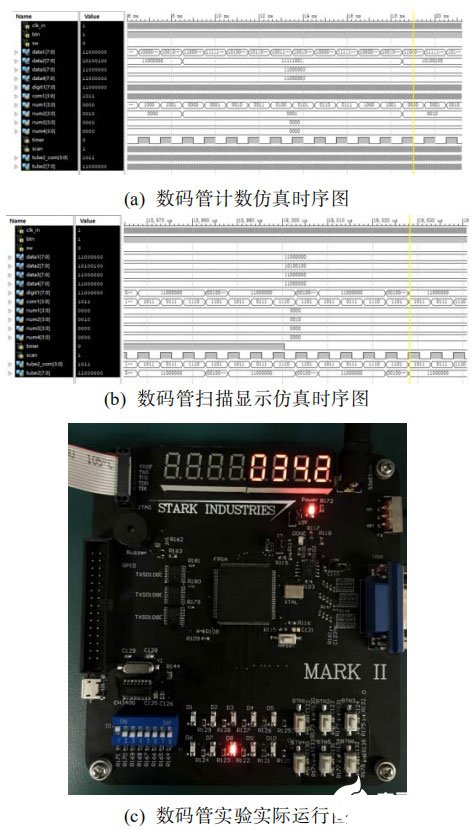

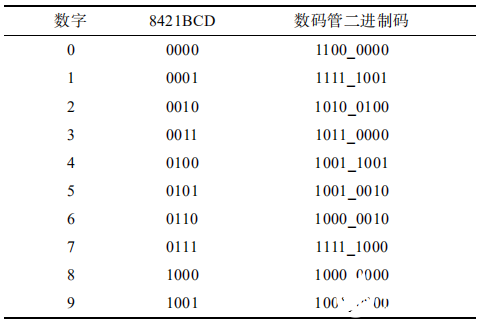

FPGA 代码设计思路如下:将系统的 50 MHz 时钟分频为 50 Hz 的逐位扫描时钟和 10 Hz 的计数时钟,最低位通过 10 Hz 的时钟进行计数,计数使用8421BCD 码表示,并转化为数码管显示的 8 位二进制代码输出。由于是共阳极数码管,当引脚公共端高电平,其他引脚为低电平时,对应的 LED 才会亮。数码管二进制码的最高位为小数点位。实验仿真及实际运行效果见图 8。

图 8 数码管仿真时序图与数码管实验实际运行图

由于实际仿真时间过长, 因此在仿真时缩短了计数的时间。表 1 为 BCD 码与数码管二进制码对应表。

表 1 数字的 BCD 码与数码管二进制码对应表

3.2蜂鸣器控制实验

实验要求通过编程控制无源蜂鸣器,使之在输入不同频率的 PWM 波情况下,发出不同音调频率的声音。

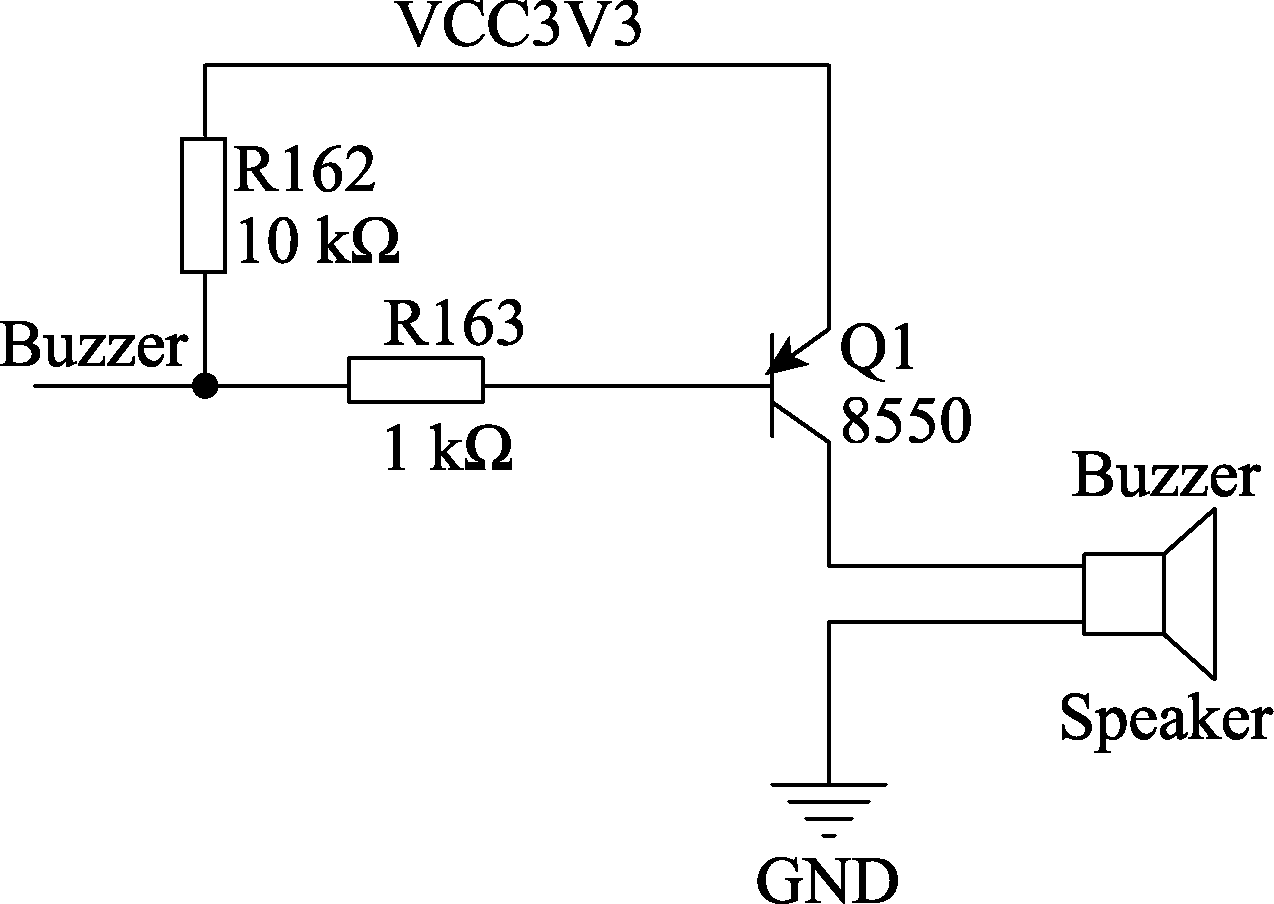

3.2.1实验硬件电路

无源蜂鸣器的硬件电路设计见图 9。

图 9 蜂鸣器电路图

3.2.2FPGA 代码设计

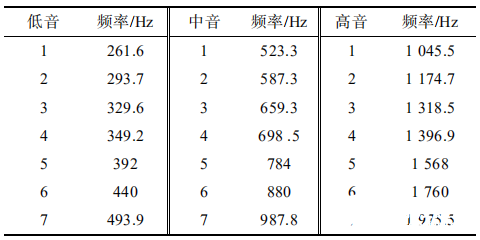

无源蜂鸣器输入不同频率的 PWM 会发出不同频率的声音,频率和音调对应见表 2。

表 2 频率和音调对应表

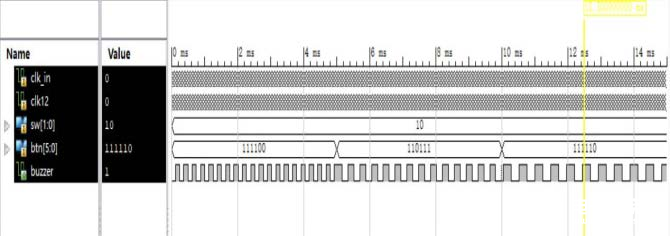

通过 ISE 的 Clock Wizard 将 50 MHz 的系统时钟频率分频为 12 MHz,然后通过计数输出不同的频率, 计数的上限值由拨码开关和按键控制,拨码开关用于选择 3 个音调,按键用于选择各个音调下的 7 个不同频率,以此实现输出不同音调频率的声音。图 10 为蜂鸣器控制仿真图。

图 10 蜂鸣器控制仿真图