系统结构

整个系统主要由n台PC基站、m&TImes;n台手持移动终端(每台PC基站负责m台手持移动终端)组成。其中PC基站以USB2.0为核心,通过蓝牙无线传输协议实现手持移动终端与基站的高速通信。手持移动终端以TMS320VC5402为核心实现系统控制,以TMS320C6713为处理器实现JPEG2000图像编码算法。

系统硬件设计

硬件结构

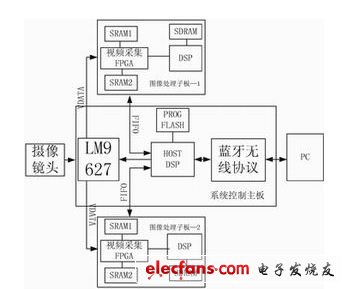

如图1所示,整个系统采用类似于PC104的栈式结构,主要由LM9267摄像头、图像处理子板和系统控制主板三个部分组成。LM9627模块设计为了提高系统的可扩展性,本系统把摄像头作为单独的一个模块设计,主要包括模拟部分、数据接口和控制接口三个部分。其中J2为数据接口,连接到图像处理子板的FPGA上;J1为控制接口,连接到系统控制主板上。图像处理子板图像处理子板由采集控制协处理器FPGA、C6713和两片“乒乓”工作的SRAM组成。两片视频 采集FPGA芯片EP1C6Q240分别采集奇数帧和偶数帧(每帧包含奇数场和偶数场)图像,每个FPGA对LM9627的视频流进行格式分析,将相应的 RGB分量转换为YUV分量,并以4:1:1的格式存储在SRAM内。两片SRAM以“乒乓”的方式工作,即同一时刻一片用于采集视频图像,另一片用做 DSP的图像缓冲区。两片C6713实现复杂的JPEG2000压缩算法。为了后续的扩展,使得C6713能够处理更大尺寸的图像,每片DSP扩展16MB的SDRAM,SDRAM以100MHz的频率工作,满足图像压缩过程中大量数据交换的要求。

图1 系统硬件框图

系统控制主板

系统控制主板以DSP C5402为核心处理器,主要负责三个任务:通过 控制LM9627摄像头;让多块图像处理子板协调工作,通过MailBox—FIFO读取它们的压缩结果;将读取的压缩结果按照蓝牙协议发送到PC基站。 为了满足高的数据交换速度,主处理器TMS320VC5402以100MHz工作,一边通过MailBox—FIFO读取压缩结果,一边将读取的压缩结果 按照蓝牙协议发送到PC基站,从而实现JPEG2000的实时压缩与解码显示。

系统软件设计

图像采集软件设计为了让系统做到实时,可通过LM9627的I2C控制总线让它工作在隔行扫描方式,则输出640&TImes;480分辨率的图像数据。而场频,则: 帧频 (隔行扫描),行频。本文采用Verilog HDL语言,实现了LM9627的实时图像采集。C6713上JPEG2000算法设计本系统的JPEG2000编码算法在C6713上的开发包括两个阶段。

算法实现第一阶段:

用C语言模拟DSP的JPEG2000算法,以判断代码的正确性,验证JPEG2000算法的复杂度、可靠性,以及JPEG2000自身的压缩性能。本系 统的JPEG2000编码器包括小波变换(wavelet)、熵编码(MQenc)、码率控制和打包(rateallocaTIon)三个主要模块。 LM9627输出为RGB,把它转化为Y:U:V=4:1:1的视频数据流,分别对三个分量进行DC位移、小波变换、熵编码,然后将三个分量所有码块的编 码流根据码率控制要求进行分层组织,其中包括码流截断操作,编码器的输出即是打包后的分层位流。进行DC电平位移(预处理)的目的是为了在解码时能够从有 符号的数值中正确恢复重构无符号采样值。传统小波变换的运算量相当大,而且往往将8位图像数据变换为浮点型,在编码中引入量化失真,不利于图像数据的无损 压缩,因此JPEG2000主要采用基于UMDFB(抽2取1滤波器组)提升小波算法。其优点在于速度快、运算复杂度低、所需的存储空间少,而且得到的小 波系数与使用传统小波变换得到的结果相同。

JPEG2000选用两种滤波器:LeGall5/3滤波器和Daubechies9/7滤波器。考虑到本系统的实时性要求以及无损压缩需求,选用5/3 小波运算。当小波分解级数提高的时候分解系数的能量更为集中,但小波分解级数的提高会使编码效率有所下降,对于本系统,4CIF(704&TImes;576)分辨率 采样图像进行5级小波分解,CIF(352×288)图像进行4级小波分解就足够了。由于采用整型模式运算,所有的量化步长均被置为1,即量化过程可以忽略。多分辨率支持可通过小波变换来实现,多失真度支持则可通过熵编码来解决。

传统Huffman编码采取依次对每个系数进行熵编码的方式;JPEG2000编码系统则是将小波变换后的子带划分成小的码块,并将码块中的小波系数组织 成若干位平面进行编码。以“位平面”为编码元,有两点好处:可以更好地利用图像局部的统计特性,为随机获取图像压缩位流提供支持;有助于提高压缩码流的抗 误码性能。在进行块编码时,JPEG2000强调多截断点的支持,截断点越多,表明图像可提供更多的质量选择。如果对每个码块仅进行位平面编码,那么对于 数据最高位数为N的块,最多可得到N个截断点。很多时候这种截断是粗糙的而且截断点数目过少。为了获得更多的截断点,EBCOT引入“编码通道”的概念, 将每个位平面进一步分成子位平面(编码通道)。在JPEG2000编码系统中使用三个编码通道:有效性通道、幅度细化通道和清除通道。这样对某个码块Bi 来说,可能的截断点可以有3N个。进行位平面编码时,JPEG2000采用的是快速自适应二进制算术编码。

算法实现第二阶段:

编写JPEG2000汇编代码,并抽出对性能影响比较大的代码段进一步优化。TMS320C67l3基于TI的VLIW技术,利用VLIW结构设计程序可 以充分利用DSP多个功能单元并行工作的特性。DSP的每一个通道都有四个功能单元(L、S、M、D),每个功能单元负责完成一定的逻辑或者算术运算,另 外A、B两个通道的互访可以通过交叉单元1x、2x完成。TM320C6713的大部分指令都可在单周期内完成,可以直接对8/16/32位数据进行操 作。同时,它最多可以有8条指令并行执行;所有指令均可条件执行。

以上所有特点提高了指令的执行效率、减小了代码长度、提高了编码效率。C6713只有两个D单元负责数据存取,在一个时钟周期中最多有两条数据存取指令并 行执行,并且从存储区取数据的LDB/LDH/LDW指令有4个时钟周期的延时,严重影响了CPU的效率。为此在编码时应尽量减少从存储区中取数据的次 数。 例如在小波变换中,我们在对SRAM里的8位采样值数据进行取操作(LDB)时,可以充分利用C6713的32位寄存器,一次从存储区中取地址相邻的4个 8位数(用32位操作指令LDW),然后分别进行运算,这样就充分利用了CPU的资源,减少了4倍的数据存取量。流水线操作是DSP实现高速度、高效率的 关键技术之一。当一条指令的处理已经准备好后到流水线的下一级,但是那一级却还没有准备接收新的输入时,流水线冲突就不可避免。

流水线冲突可以分为三大类:跳转冲突、寄存器冲突和存储器冲突。为解决流水线冲突问题,在使用汇编语言时需要特别注意C6000指令的延迟情况,有些指令 并不是立刻就能得到结果。此外,为了保证代码效率,必须提前知道每一条指令的运行周期数,并提前安排该指令或重新调整指令顺序。只有尽量将这些指令的前后 指令放在它们所需的延迟间隙内并行执行,才能达到减少等待周期、提高程序效率的效果。经过C语言模拟算法到全汇编实现的优化,然后再对汇编代码进行优化, 使得系统的性能大大提高。