摘要:传统的插值算法在视频图像缩放尤其是输出高分辨率的视频图像时,对细节方面的处理性能较差。采用多相位插值算法实现视频图像缩放,主要阐述算法的原理及算法实现的硬件结构。其中硬件电路控制部分使用Xilinx公司的Spartan6系列FPGA芯片,系统可以实现将四路摄像头采集的视频信号从任意通道放大到1 920x1 080@60 Hz的分辨率显示,结果表明输出视频图像的实时性和细节保持良好。

0引言

视频图像缩放又可以称为视频图像分辨率的转换、视频图像的重采样、视频图像的尺度变换等,是数字视频图像处理技术中的关键技术之一,直接影响着视频图像输出质量效果和视觉体验。目前视频图像缩放技术广泛应用于医学图像、工程学、多媒体、视频会议等领域[1]。

传统的视频图像缩放插值算法有最近邻插值、双线性插值、双立方插值等,其他的插值算法还有边缘插值、B样条插值、自适应插值等,其中基于线性模型的算法在应用于图像处理时高频信号会叠加到低频信号区域,导致输出视频图像出现混叠情况,尤其是视频图像输出分辨率要求较高时细节方面的处理会带来较差的视觉体验效果。多相位插值算法也是一种常用的视频图像缩放方法,其相对于传统的插值算法而言,在细节保持上具有较好的性能,也被广泛用于工业界。

1算法原理

视频图像缩放的基本原理是将分辨率为(M,N)的原图像转换成分辨率为(X,Y)的目标图像。用数学定义可以描述为:已知(M,N)个像素点,Pixelin(i,j)(i=1,2,…,M;j=1,2,…,N),其中i,j为原图像的像素点坐标,Pixelin(i,j)为原图像像素值。现在希望通过一个数学关系式的映射,利用已知像素点求得输出像素点,Pixelout(x,y)(x=1,2,…,X; y=1,2,…,Y),其中x,y为目标图像的像素点坐标,Pixelout(x,y)为目标图像像素值。那么输入输出图像的像素值对应函数关系可以表示为:Pixelout(x,y)=f(i,j, Pixelin(i,j)),多相位插值的本质就是根据函数的映射关系求解目标图像的像素值。

根据上述分析知,目标图像像素值并不能直接从原图像获取,而是需要通过原图像相关的位置坐标、像素值等信息计算得出。由于图像内容的局部相关性,输出目标图像的像素值和相应空间位置邻近的输入原图像像素值相关性较大,与空间位置较远的像素值相关性较小。一般的视频图像缩放处理是典型的二维滤波的过程,可以用公式表示[4]如下:

Pixelout(x,y)=

∑HTaps-1i=0∑VTaps-1j=0Pixelinx-HTaps2+i,y-VTaps2+j&TImes;

Coef(i,j)(1)

式中HTaps和VTaps为两个二维滤波器在水平和垂直方向上的抽头数,Coef(i,j)为对应滤波器的系数,这个系数代表了参与运算的输入像素值对输出像素值的权值大小。它的值确定了相应位置输入像素值对输出像素值的影响并直接决定缩放的效果,系数的确定取决于滤波器低通和抗混叠等需求。

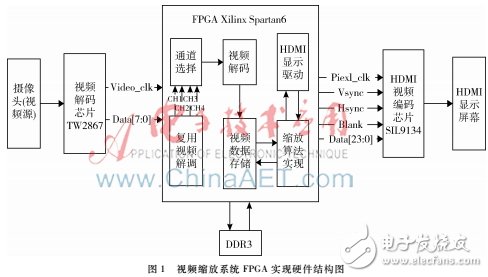

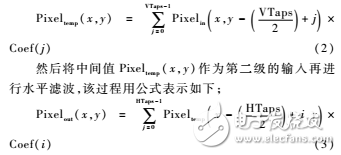

图1视频缩放系统FPGA实现硬件结构图二维结构在数据运算时比较复杂,为了简化运算一般将二维滤波器进行拆分,使用两个一维滤波器级联来实现二维特性,即水平滤波器和垂直滤波器。首先第一级进行垂直滤波输出中间值Pixeltemp(x,y),该过程用公式表示如下:

通过以上分析可知,简化运算前后需要的乘法器个数从(VTaps&TImes;HTaps)减少为(VTaps+HTaps)个,运算量大大降低,这种方式非常有利于实现实时性要求较高的硬件系统。同时这个思路也是各种视频图像缩放算法硬件实现的基本模型,即在水平方向和垂直方向分别进行缩放处理,这样问题就成了一维信号采样率变化的分析处理过程。

2系统硬件结构

系统硬件结构如图1所示,使用Xilinx公司的Spartan6系列FPGA芯片对多相位插值缩放算法进行验证。系统采用四路模拟摄像头采集视频信号作为输入源,通过TW2867多路视频解码芯片将模拟视频信号转化成数字视频信号送给FPGA芯片进行数据处理,FPGA首先对输入的数据信号进行一定的预处理,由于采集的图像与输出显示的图像刷新率不一致,为了保证数据处理时读写速率的匹配,需要将图像数据写入DDR3然后读取数据进行缩放处理再输出,输出的信号需要符合HDMI标准时序,最后通过SIL9134视频编码芯片将输出数据信号编码成视频流传输到屏幕显示并查看输出的效果。

2.1相关芯片介绍

2.1.1视频解码芯片