基于FPDP的高速数据传输系统设计

随着电子技术的高速发展,越来越多的信号处理系统,需要高速的数据采集和大吞吐量的数据传输,来实现数据的高速实时处理能力。在雷达系统中,原始数据中包含丰富的信息,及时获得原始数据并进行实时分析就显得尤为重要,因此在雷达处理机中需要大量使用板间通信,并保证板间数据传输具有高速性和可靠性。单板系统已经不能满足需求,需要多板共同实现。

FPDP总线可用于两个或多个VME板之间的高速数据传输,其数据传输速率可达160 MB/s。FPDP总线位于VME板卡的前面板,完全不影响位于背板插槽的VME总线。在实际应用中,一块VME板卡允许有多个FPDP端口。因此,在雷达系统中,可使用FPDP总线必将提高数据传输和处理能力。

1 FPDP总线概述

FPDP(Front Panel Data Port,前面板数据端口)总线最初是由加拿大的InteracTIve Circuits and Sys-tems Ltd(ICS)公司开发,后经VSO(VITA Stand-ards OrganizaTIon)组织提出并形成标准协议。FPDP总线是32位的并行同步总线,通过80芯的扁平连接电缆进行板间连接。主要用于两个或多个 VME总线板卡间进行高速数据传输。

FPDP总线上的设备可以有:

(1)FPDP主发送设备(FPDP/TM:FPDPTransmitter Master),主发送设备是数据传输的源端,并产生所有其他板需要的时钟及相关时序信号;

(2)FPDP主接收设备(FPDP/RM:FPDP Re-ceiver Master),主接收设备是数据传输的末端,用于接收数据和终止控制信号;

(3)FPDP接收设备(FPDP/R:FPDP Receiv-er),接收设备只是接收数据,没有终止控制信号,允许数据传输继续下去。

FPDP总线上必须至少有一个主发送设备和一个主接收设备。但可以有多个接收设备,从而可以实现“多点”传送。在某一时刻,总线中只有一个主发送设备,传输以单方向进行,故在总线上的设备之间也就不存在总线的竞争和冲突问题。所以FPDP总线协议不包含地址和仲裁周期,从而可以实现高速数据传输。

虽然FPDP总线为单向传输,但可以通过硬件链路开关或者软件手段对FPDP总线的发送设备与接收设备进行配置,实现分时复用的双向数据传输。

2 设计实例

在雷达系统中,原始数据(有关目标的距离、方问、速度等状态参数)的变化对于成像结果有着十分重要的影响。因此能不能够实时传输采集到的原始数据并进行有效分析,将直接影响到成像质量的好坏。

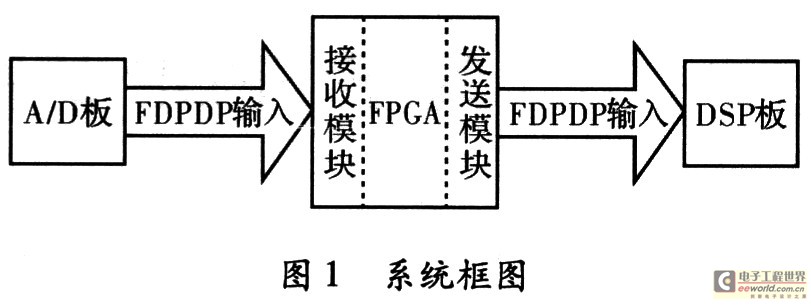

在该设计中,FPGA的数据通道采用FPDP总线结构,分别与A/D板、DSP板相连,进行实时高速数据传输。A/D板负责对回波信号进行高速采集,DSP板接收FPGA发送过来的合成数据进行后期处理。FPDP接收模块负责接收来自A/D板的原始回波数据,FPDP发送模块负责把原始回波数据及其他飞机参数打包并以FPDP协议的形式发送给DSP板。如图1所示。

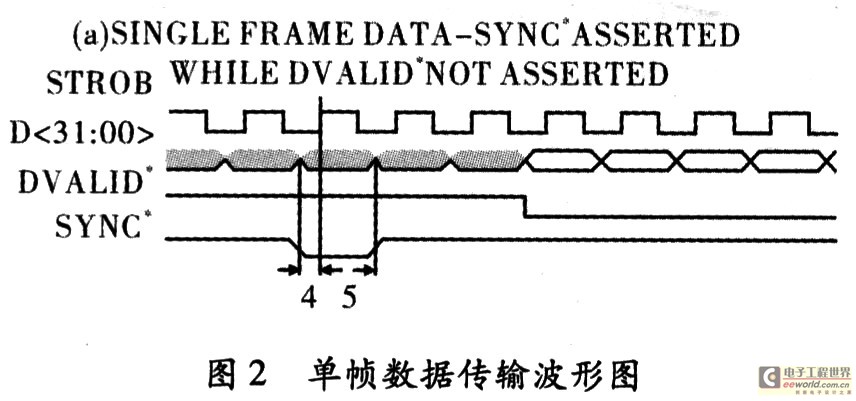

A/D板与DSP板的数据接口均为FPDP总线结构,发送方式为单帧模式。对于单帧数据传输模式,同步信号SYNCn应该先于第一个发送的数据,此时数据有效信号(DVALIDn)仍为高,指示数据无效。在进行数据传输时,将DVALIDn信号有效,在时钟STROB(或PSTROBE)上升沿的同步下将发送数据驱动到FPDP的数据总线上。在时钟STROB(或PSTROBE)上升沿,接收设备对D[31..0]和DVALIDn信号进行采样。若 DVALIDn为低,则认为发送过来的数据是有效的。单帧数据传输波形图,如图2所示。

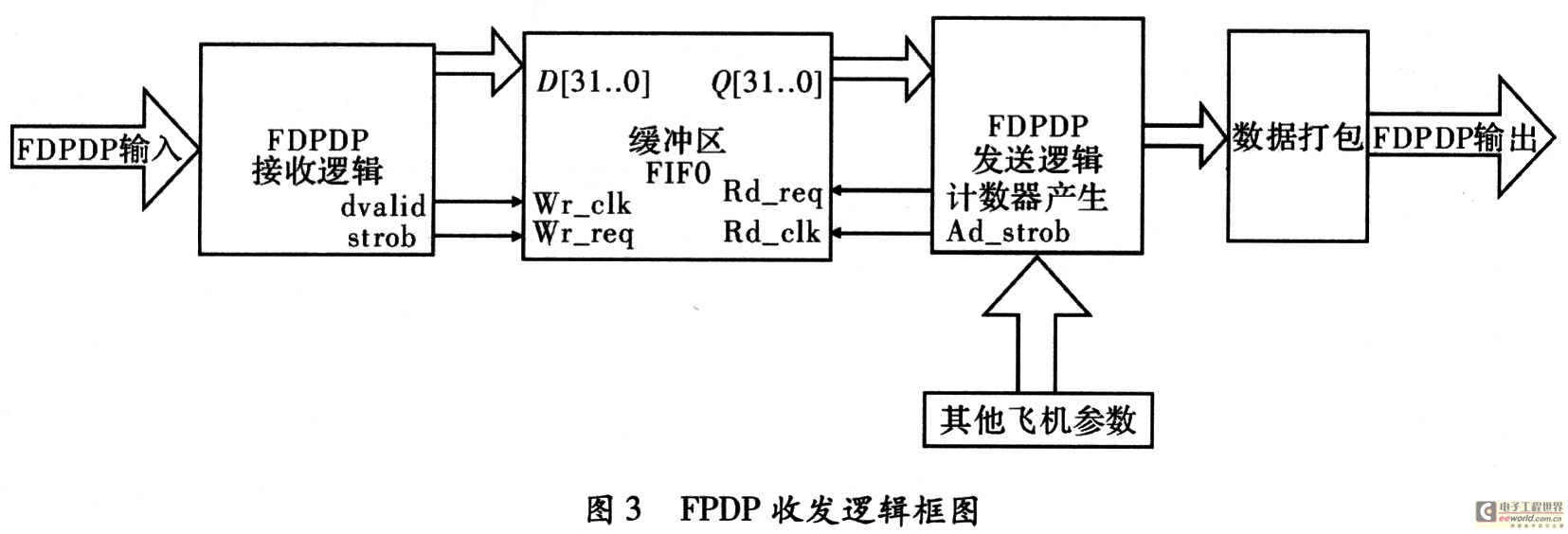

为了满足信号处理机实时处理的要求,要求输入到DSP板的原始数据符合处理的数据格式。而采集到的数据需按一定格式打包,称为数据合成。FPGA要将来自不同设备的数据合成为所需的帧格式后转发到DSP板。这样,DSP板在获得数据帧后就可以直接进行处理而不必再有格式转换的开销。其原理图,如图3所示。

由于FPDP总线传输实时性要求很强,在传输过程中不允许数据丢失,具有数据量大、传输速度高等特点。因此,FPDP接收逻辑应在接收到原始回波数据后,尽快发送给DSP板。否则,将造成数据堵塞、丢失及紊乱,严重影响后端的成像处理,因此在FPDP总线收发逻辑之间引入一个数据缓冲区FIFO,暂存原始回波数据。

FPDP接收逻辑接收来自A/D板的回波数据,主要负责对数据缓冲区FIFO的写入操作。其工作流程如下:在FPDP总线数据有效(DVALIDn为低) 时,FIFO的写请求Wr-req信号有效,此时数据随着写时钟信号(Wr-clk即AD板发送过来的Ad-strob信号)写入FIFO。若FPDP总线数据无效,此时FIFO的写请求信号也无效,数据不能写入FIFO。

FPDP发送逻辑接负责将回波数据和其他飞机参数按照一定的格式打包,并经由FPDP总线发送出去。其工作流程如下:FIFO的读请求Rd-req信号由发送时序计数器产生,当计数器的计数值为一定值(A/D采集满一帧数据)时,Rd-req有效,随着读时钟(Rd-clk即A/D板时钟 AD_strob)信号,数据从FIFO中读出,此时计数器清零。数据按一定格式打包后,按FPDP单帧传输模式将打包数据送入DSP板。

FPDP发送逻辑应当在FPDP同步信号SYNCn到来后立即启动数据发送,这样大大增强了数据传输的实时性和可靠性。值得注意的是,A/D板传来的第一组回波数据来不及打包传送给DSP板,因此要在FIFO中累积一组回波数据后再开始往DSP板发送数据,这样每次发给DSP板的一帧数据中,回波数据应为上一次A/D板发来的数据,这样可以保证不丢失回波数据,只是最后一组回波数据仍然会存在于时序板中,采集不到,应当丢弃。

特别地,由于模块的输入输出功能已确定,所以作为A/D板接收端的方向信号DIRn不被使用,而作为DSP板发送端的DIRn信号则常接低。对于输入的 SUSPENDn和NRDYn信号,A/D采集板对NRDYn信号不响应,所以FPGA对这两个信号也不响应,避免干扰AD采集板的数据采集。

3 设计仿真

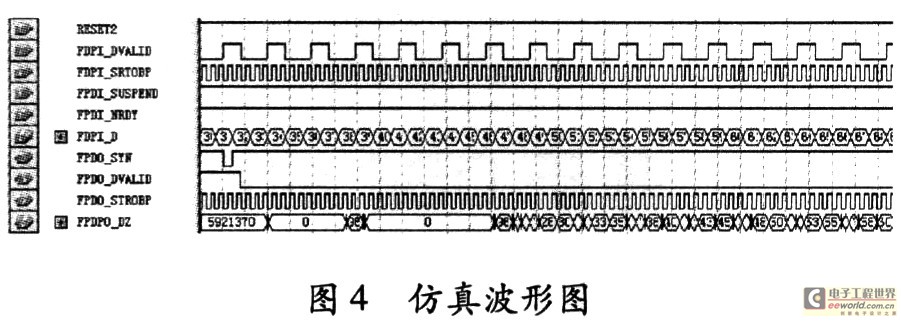

以下给出了基于Quartus 6.0的一段波形仿真图,如图4所示。

如图4所示,为FPDP发送逻辑的仿真图,其中FPDI_SUSPEND和FPDI_NRDY始终无效(为高),在发送数据前FPDO_SYN先有效(为低),此时FPDO_DVALID仍无效(为高)。在传输数据时,FPDO_DVALID有效(为低),在时钟FPDO_STROBP的上升沿将数据通过 FPDP总线送出。

4 结束语

从以上的分析得出以下结论:

(1)该设计中,FPDP总线以其特有的前面板方式和传输机制,有效地解决了多块板卡间的高速数据传输问题;

(2)FPDP数据的高速、实时接收和发送是难点。该设计采用了一个片内FIFO缓冲区解决了此问题。片内FIFO集成度高、占用资源少,有效地解决了系统需求;

(3)该设计使用同步信号作为接收帧的有效标志,提高了系统的实时性和可靠性。