FPGA的B超成像系统图像采集的原理和实现

1、引言

医学超声诊断成像技术大多数采用超声脉冲回波法,即利用探头产生超声波进入人体,由人体组织反射产生的回波经换能器接收后转换为电信号,经过提取、放大、处理,再由数字扫描变换器转换为标准视频信号,最后由显示器进行显示。在基于FPGA+ARM 9硬件平台的全数字化B超诊断仪中,前端探头返回的回波电信号需由实时采集系统进行波束合成、相关处理、采集并传输至ARM嵌入式处理系统,视频信号数据量大,实时性要求高,因此选用FPGA+SRAM构成实时采集系统,在速度和容量上都能满足上述要求。主要介绍B超成像系统中应用FPGA进行逻辑控制进行超声视频图像采集的原理和实现。

2、系统构成工作原理

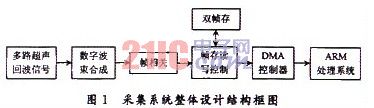

如图1所示,采集系统首先由数字波束合成器对多通道超声回波信号进行波束合成,数字波束合成器对不同通道信号进行延时,使同一点的信号同相相加,同时对多个通道的回波信号进行空间域上的加窗,类似匹配滤波,可以提高信号的信噪比。然后对合成后的超声视频信号做一个帧相关的预处理,即图像帧与帧之间对应象素灰度上的平滑处理。因为叠加在图像上的噪声是非相关且具有零均值的随机噪声,如果在相同条件下取若干帧的平均值来代替原图,则可减弱噪声强度。在帧相关过程中,FPGA要控制数据的读取、处理以及存储。在为了满足视频显示的实时性,该采集系统采用双帧存结构的乒乓机制,由FPGA实现读写互锁控制。经帧相关处理完后的视频数据交替写入帧存A和帧存B,帧存读控制器根据后端处理速度读取帧存中的数据,送往DMA控制器,DMA控制器开启DMA通道进行数据传输。FPGA实现读写控制时,为了避免同时对一个帧存进行读写操作,需要设置读写互斥锁进行存储器状态切换。

3、系统设计与实现

3.1 数字波束合成

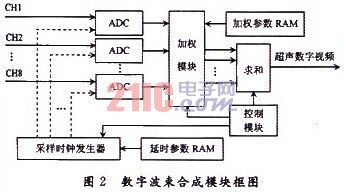

对于具有128阵元和32收发通道的超声探头,在进行32路AD转换后,将其分为4组,每组8路接收通道,每组用一片FPGA实现,在该FPGA内首先进行接收延时和动态聚焦再进行加权求和,其后再进行组间的求和产生超声数字视频信号。每一组的系统框图如图2所示:

对不同通道的回波信号进行不同的延时是达到波束聚焦的关键,延时按精度可分为粗延时和细延时:粗延时用于控制A/D采样的开始时间,精度为32 ns,延时参数由FPGA的片内RAM中读出,更换探头时系统控制器将相应数据写入这些RAM;细延时由采样时钟发生器根据不同的通道产生不同的A/D采样时钟,这些时钟的相位互相错开,其错开的值刚好等于各阵元传播延迟之差。考虑到系统的实时性以及探测过程中深度的变化,需要采用动态聚焦。动态聚焦是在A/D采样开始后,通过读取动态聚焦参数,在采样的过程中控制采样时钟发生器实现。

8个通道的回波信号经过A/D采样后,送入FPGA,缓冲之后同步读出进入加权模块,加权模块由8个无符号为数字乘法器组成。回波信号分别与加权参数相乘后得到具有动态聚焦和加权特性的数据。8组数据再经过3级加法器就得到波束合成之后的超声数字视频数据。

3.2 帧相关处理

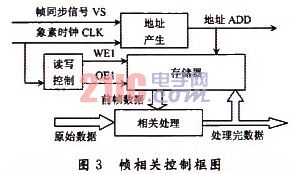

帧相关模块如图3所示,由帧相关控制器和一片存储器组成,进行帧相关的存储器采用大小为256 kB的静态存储器(SRAM)。帧相关控制器由FPGA实现,完成地址产生、存储器读写控制、帧相关计算功能,因为实时性的要求,即保证送往后端双帧存的数据不能中断,所以考虑到对逐个象素数据读写的同时就进行相关处理,而且需要在同一个象素时钟周期内完成。读写控制器在1个象素时钟周期的前半段需要读出存储器中的数据和当前帧数据进行相关处理;时钟周期的后半段再将相关处理完的数据写入存储器以备后用,这样送往后端双帧存的数据依然是和象素时钟对应的连续象素数据。

帧相关的工作流程如下:

(1)地址产生。地址的产生由一个象索计数器实现,输入信号为帧同步信号VS和象素时钟CLK。前端提供的帧同步信号VS为该计数器的复位信号,在每一帧的开始,计数器清零,然后根据象素时钟CLK计数生成地址,每个象素时钟周期内地址不变,依据此地址进行存储器的读写。

(2)读取已有数据及相关处理。在一个象素时钟周期的前半段,也就是CLK跳变为高电平时,读写控制器输出的读信号OEl为有效,读出前帧中一个象素的数据,送到FPGA内部实现的加法器的A口,与同时到达B口的当前帧的对应象素数据相加平均。

(3)数据保存及传输。在同一个象素时钟周期的后半段,也就是CLK跳变为低电平时,读写控制器输出的写信号WEl为有效,相关处理完的数据写回原来的地址,同时该数据也送往帧存写控制模块。

3.3 帧存乒乓读写控制机制

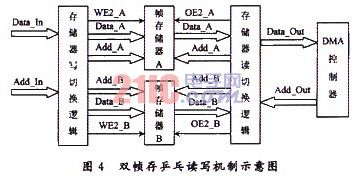

超声视频图像需要实时地采集并在处理后在显示器上重建,图像存储器就必须不断地写入数据,同时又要不断地从存储器读出数据送往后端处理和显示。另外,为了满足这种要求,可以在采集系统中设置2片容量一样的帧存,通过乒乓读写机制来管理,结构如图3所示。为了确保任何时刻,只能有1片帧存处于写状态,设置1个写互斥锁;同时,只能有1片帧存处于读状态,设置一个读互斥锁。在系统初始时,1片帧存为等待写状态,另1片为等待读状态;开始工作后,2片都处于读写状态轮流转换的过程,转换的过程相同,但是2片状态相错开,这样就能够保证数据能连续地写入和读出帧存。该机制如图4所示,工作流程为:

(1)采集过程未开始,帧存A为等待写状态,获得写互斥锁;帧存B为等待读状态,获得读互斥锁;

(2)帧存写控制器收到一帧开始信号,判断为采集开始,设置帧存A写信号WE2 A有效,帧存A开始写入当前帧数据;同时帧存读控制器设置帧存B读信号OE2_B有效,帧存B则开始读出所存数据;

(3)一帧结束,帧存A写结束,释放写互斥锁;帧存B读结束,释放读读斥锁;

(4)等待另一帧开始,帧存A获得读互斥锁;帧存B获得写读斥锁;

(5)另一帧开始,写控制器设置帧存B写信号WE2B有效,帧存B开始写入数据;读控制器设置帧存A读信号OE2 A有效,帧存A则开始读出数据。

3.4 DMA传输

对整个B超诊断仪来说,系统要完成视频图像数据的实时采集和指定的处理,高性能ARM处理器的处理能力可达每秒数百万条指令,因此数据的传输设计是提高系统速度的关键环节。ARM处理系统与外部的数据传输可以通过CPU访问外部存储器的方法实现,但是效率低下,不能满足系统实时性的要求,而DMA数据传输以不占用CPU时间和单周期吞吐率进行数据传输的优点在实时视频图像采集系统中得到广泛的应用。但是因为DMA的传输速率和前端视频图像数据的输入速率不匹配,很难发挥出DMA数据传输的优势。由可编程的FPGA控制SRAM组成的双帧存可以很好地解决这个问题;此外,FPGA内部嵌入了一定数量的RAM,可以经过配置成缓冲存储器,通过灵活的逻辑结构可以方便地实现对输入输出数据流的控制,成为连接ARM处理系统和SRAM的纽带和桥梁。

4、结语

在B超数字视频图像实时采集系统中采用FPGA作为采集控制部分,首先可以提高系统处理的速度及系统的灵活性和适应性:由于在FPGA和ARM处理系统之间采用SRAM做数据缓冲,并用DMA方式进行传输,大大提高系统的性能;由于采用FPGA可编程逻辑器件,对于不同的超声视频信号,只要在FPGA内对控制逻辑稍做修改,便可实现信号采集;FPGA的外围硬件电路简单,因而在硬件设计中,可以大大减小硬件设计的复杂程度。而FPGA的时序逻辑调试可在软件上仿真实现,因而降低硬件调试难度。