半导体产业长期以来奉“越小越好”为真理,但随着工艺技术不断向纤小型方向发展,功率问题也不断出现,导致技术发展出现了瓶颈。互补金属氧化物半导体(CMOS)工艺技术是现代微处理器与数字信号处理器(DSP)产品所采用的主导技术。CMOS制造工艺技术从90纳米向65纳米乃至更小型方向过渡,芯片密度不断提高,静态与动态功耗常常会超过可接受的数值。采用电压缩放技术可解决上述问题。

??????? 折中管理

??????? 根据摩尔定律,芯片级的晶体管密度和芯片复杂性每24个月就会翻一番,而集成电路的性能也将相应提高。因此,能够在相同或更低的面积上集成更多的功能,并以更低的成本,实现更多的特性以及更高的速度。

??????? 与任何受益与摩尔定律的其他芯片类型一样,DSP也实现了一系列新型多媒体应用,如便携式媒体播放器、智能电话与各种影像设备等。同时,电信、无线通信以及网络领域的基础设施应用也受益匪浅。

??????? CMOS技术是现代DSP与微处理器设计的常用技术。与其他技术相比,该技术的处理与缩放更为简单易行。此外,它还可提供良好的性能功耗比。

??????? 尽管高级技术的缩放可在单位面积上实现更多的元件数量与更高的功能,但单位面积的功率(功率密度)也在同时增加。随着硅芯片技术的稳步发展,推动CMOS工艺向65nm技术节点甚至更小的结构尺寸方向发展,芯片级的静态与动态功率问题也日益突出。

??????? 静态功耗是指器件上电闲置时的功耗,即没有晶体管开关情况下的功耗。因此,静态功耗与工作负载和使用情况无关。静态功耗的主要来源在于漏电流IL,而影响漏电流的主要因素则是晶体管的类型,其中包括物理尺寸(长度、宽度)以及硅芯片制造工艺技术的各种特点等(如氧化层的厚度、掺杂配置)。

??????? 在晶体管方面,静态功耗PS等于电源电压Vss与IL的乘积。造成漏电流的因素为晶体管关闭时的次阈值漏电流(I)、结漏(IL、J)以及隧道漏电流(IL、GT)等。请参见图1。

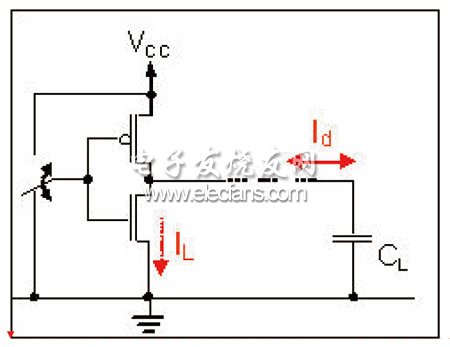

??????? 另一方面,动态功耗则是时钟速度(晶体管开关速度)和晶体管电容负载的函数,它也取决于物理晶体管的尺寸。更具体地说,我们可以看到,I=CdV/dt,而PD=ID,Vcc=CfVcc2,这里的C为电容(晶体管与电线)负载,f等于开关频率,而Vcc则等于电源电压。理想情况下,静态功耗为零,这样总功耗就为PD。

??????? 图2显示了通过CMOS逆变器的漏电流和动态电流。采用高级工艺技术节点的情况下,静态功耗的增幅比动态功耗的增幅更快。

?图1 具有漏电流现象的NMOS晶体管单元

图2? 具有电容负载的CMOS逆变器