在特定的故障机制中,BSI传感器的寿命比FSI短150-1,000倍。

LFoundry和意大利罗马的Sapienza大学在IEEE电子设备学会期刊上发表了一篇开源论文——“《背面照明配置下CMOS图像传感器的性能和可靠性下降》,作者:AndreaVici,FeliceRusso,NicolaLovisi和AldoMarchioni,安东尼奥·卡塞拉和费尔南达·伊雷拉。

该论文中数据显示,在特定的故障机制中,BSI传感器的寿命比FSI短150-1,000倍。当然,可能还有许多其他故障源掩盖了这一巨大差异。

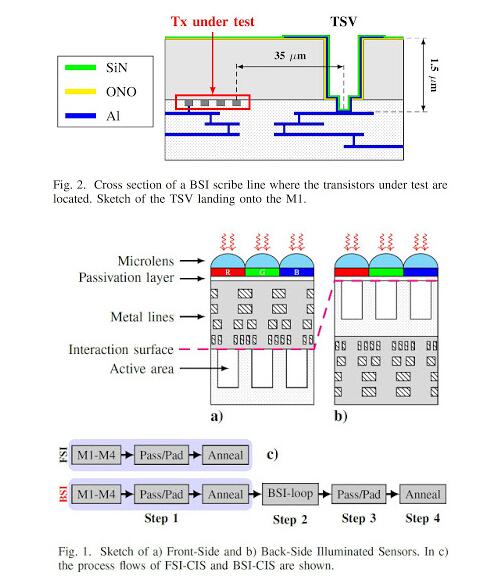

”我们提出了背面照明的CMOS图像传感器中晶圆级可靠性专用测试结构的系统表征。在制造工艺流程的不同步骤进行的噪声和电学测量结果明确表明,背面照亮配置的晶圆翻转/键合/变薄和VIA开口会导致形成类似氧化物供体的边界陷阱。相对于常规的前侧照明的CMOS图像传感器,这些陷阱的存在会导致晶体管的电性能下降,改变氧化物电场并改变平带电压,并严重降低可靠性。随时间变化的介电击穿和负偏置温度不稳定性测量结果概述了这些边界陷阱对寿命预测的影响。”

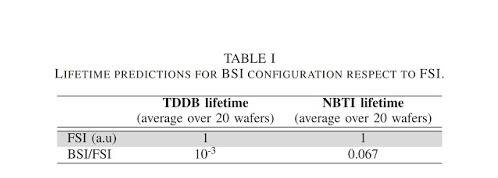

“TDDB测量在125℃,N沟道的Tx进行,施加栅极电压应力Vstress为+7.6V.对于每个Vstress几个样品进行了测试,并测量采用所限定的三个标准的时间。击穿在JEDEC标准JESD92中,对于每种应力条件,击穿时间值的Weibull分布的拟合给出了相应的失效时间(TTF)。用功率定律(E模型)推断对数-对数标度和工作栅极电压下的寿命。

NBTI测量是在125℃,p通道Tx上进行的,施加的Vstress为-3至-4V,并多次测试了几个Tx.在这种情况下,遵循JEDEC标准JESD90,寿命定义为使额定VT偏移10%所需的应力时间。VT移位具有与应力时间有关的幂定律,并且可以推断出工作栅极电压下的寿命值。”

“噪声和电荷泵浦测量表明,在栅极氧化物中存在供体状边界陷阱,在正面照明配置中不存在。陷阱密度随与界面距离的变化呈指数关系,并达到2x10e17cm的值。在1.8nm处为-3.在制造过程中的不同步骤进行的电测量表明,这些边界陷阱是在背面配置的工艺循环中产生的,该背面循环包括晶片上侧翻转,键合,薄化和VIA开口。

陷阱使氧化物电场发生扭曲,并使平带电压相对于正面配置发生偏移,就好像背面配置中存在1.6x10e-8C/cm2的正电荷重心在1.7nm处一样,从而改变了漏极和栅极电流曲线。

我们发现,类似供体的边界陷阱也会影响背面设备的长期性能。进行随时间变化的介电击穿和负偏置温度不稳定性测量以评估寿命。正如预期的那样,两种情况下边界陷阱在寿命预测中的作用是不同的,但是无论如何,相对于正面照明的CMOS图像传感器,背面的可靠性都会下降。”

但对于背面照明配置下CMOS图像传感器的性能和可靠性下降的结论,FeliceRusso却认为:

该论文作者的意图并非表明“LFoundry数据表明BSI传感器不如FSI可靠”,而是评估特定BSI流程固有的潜在可靠性失败机制,而不是强调一般的BSI可靠性弱点。LFoundry生产的BSI传感器采用了多种处理技术,超出了所有产品的可靠性要求。

广泛被接受的BSI工艺对装料效果敏感,与特定的工艺流程和生产线无关。它可能导致氧化物降解,这主要与氧化物中施主状陷阱的另外分布有关,位于距氧化硅界面(边界/慢陷阱)的隧穿距离之内,并且可能与氧空位有关。

由大学发布的这项工作基于晶片级特征数据,该数据是在2018年使用专用的测试结构收集的,该结构经过适当修改以强调BSI主要工艺步骤对陷阱产生的影响而制造的专用测试结构。

为了解决这些潜在的固有故障机制,已实施了多种工程解决方案,以满足直至汽车级的所有可靠性要求。我们较早发表的着作表明BSI可以将FSITDDB寿命与经过适当设计的解决方案相匹配。可以理解,并非所有解决方案都可以发布。

结果已被用于进一步改善BSI产品的性能,并确定用于下一代BSI传感器的后续创新解决方案。