先进驾驶辅助系统(Advanced DriverAssistance Systems,ADAS)是成长最快速的汽车应用。市场研究机构Gartner的报告估计,此市场规模将从2014年的56亿美元成长至2018年的102亿美元,在2013~2018年之间实现17.1%的年复合成长率(CAGR);ADAS相关半导体产品的消耗量同时间则将从13.8亿美元成长至24亿美元,其间年复合成长率将达到15.5%。

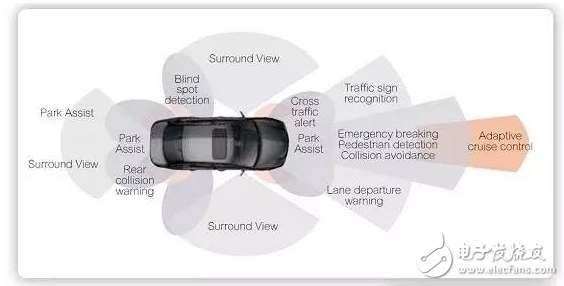

以安全性为核心的驾驶辅助系统,支持行人侦测/避让、车道偏离警报/纠正、交通标志识别、全景影像、疲劳监控等,这些应用以及其他多种应用(如图1所示),需要一种全新类别的系统单芯片(SoC)来满足该系统日益成长的需求。

在消费者利益和政府法规的推助下,为了改善道路安全性,汽车制造商正在要求一级零组件供货商(TIer 1)和半导体产品供货商去开发包含最新多媒体标准、执行多种基于视觉的算法,且结合影像和雷达系统传感器数据的SoC。

图1 各种ADAS应用。

为了实现高性能运作所需的先进通讯协议,ADAS SoC使用了比大多数高阶消费性应用更严格的尖端设计和工艺技术;这类组件的设计者仰赖IP供货商协助他们克服实现特定应用IP需求的挑战,在越来越短的设计、成形周期中满足汽车应用对强韧度、可靠性和安全性的需求。

ADAS SoC设计准则

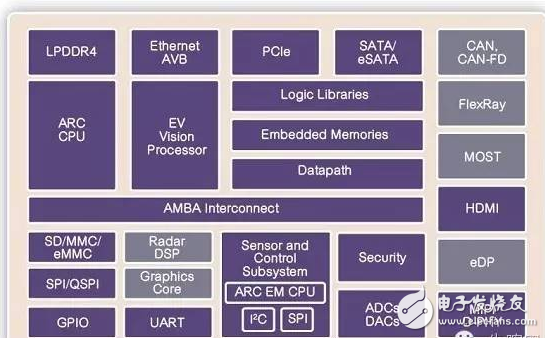

从应用和系统的两个角度来看,这类新型ADAS SoC都拥有特定的设计准则,以确保高效率的SoC设计实作;为ADAS应用构建SoC的设计人员需要结合高性能与省电的IP功能,以协助实现整体系统吞吐量,并满足实时性的服务质量要求(如图2)。

图2 采用16/14奈米工艺的ADASSoC,图中紫色部分为Synopsys的Design WareIP产品。

这类应用处理器的性能要求至少是32位、1GHz以上频率运行的处理器;实际上,支持多种基于视觉之应用的ADAS SoC已经开始转向64位。除了高性能应用处理器,这类SoC还需要一个独立的视觉处理器,实现诸如卷积神经网络(ConvoluTIonalNeural Networks,CNN)等的最新视觉算法。

此外一个附加的绘图处理器或客制化数字信号处理器(DSP)核心负责高速率像素处理,与高画质多媒体接口(HDMI)或行动产业处理器接口(MIPI)D-PHY等多媒体接口链接,同时支持尺寸越来越大的高画质显示器。为了支持提供影像和雷达/光达(lidar)数据的多个摄影机和雷达传感器,还需要一个传感器和控制子系统来为应用处理器(ApplicaTIon Processor)分担传感器数据管理任务,以实现高等级的传感器融合。

新一代ADAS SoC需要高达8GB的车规LPDDR4内存,以支持处理器应用软件,与以太网络音频桥接技术(Ethernet AVB)与时效性网络(TIme SensitiveNetworking,TSN)所提供、支持多媒体数据流量的广泛系统链接。SoC外围则提供额外的PCI Express、SATA、通用异步收发器(UART)、SPI/QSPI、CAN与FlexRay等界面。

最后,为了支持由外部Bluetooth Smart、Wi-Fi或4G LTE无线芯片实现的云端链接,ADAS SoC必须内含坚固的、以硬件为基础的安全通讯协议,以支持安全开机(boot)、安全识别与身分验证、加密以及解密。

除了IP功能是ADAS SoC设计工程师必须考虑的元素,汽车产业的一级零组件供货商及半导体SoC设计人员、架构师还需要考虑延迟、功耗、可靠性以及与工艺相关的设计挑战。

低延迟是因应实时多媒体服务等级保证的基本原则;除了低延迟,这类SoC在不断采用最新多媒体协议和关键特性─例如行人侦测与校正等特定ADAS应用所需的嵌入式视觉处理功能─的同时,还需要保持最低功耗。对ADAS SoC设计人员而言,另一项关键挑战是确保车厂所要求的高可靠性和连续运作,因此芯片需要实现关键错误检查和纠正(ECC)与同等技术。

由于需要高性能和高整合度,设计人员锁定先进半导体工艺,例如许多设计团队尚不熟悉的16/14奈米鳍式场效晶体管(FinFET)工艺节点。对于下一代汽车ADAS应用SoC而言,因应低延迟、低功耗、先进通讯协议、ECC等SoC挑战,以及16/14奈米FinFET工艺任务关键型IP的可取得性等都是关键议题。